Jeonghyun Woo The University of British Columbia Department of Electrical and Computer Engineering Vancouver, BC, Canada jhwoo36@ece.ubc.ca

> Gururaj Saileshwar University of Toronto Department of Computer Science Toronto, ON, Canada gururaj@cs.toronto.edu

## Abstract

Per Row Activation Counting (PRAC) has emerged as a robust framework for mitigating RowHammer (RH) vulnerabilities in modern DRAM systems. However, we uncover a critical vulnerability: a timing channel introduced by the Alert Back-Off (ABO) protocol and Refresh Management (RFM) commands. We present *PRACLeak*, a novel attack that exploits these timing differences to leak sensitive information, such as secret keys from vulnerable AES implementations, by monitoring memory access latencies.

To counter this, we propose *Timing-Safe PRAC (TPRAC)*, a defense that eliminates PRAC-induced timing channels without compromising RH mitigation efficacy. *TPRAC* uses *Timing-Based RFMs*, issued periodically and *independent* of memory activity. It requires only a single-entry in-DRAM mitigation queue per DRAM bank and is compatible with existing DRAM standards. Our evaluations demonstrate that *TPRAC* closes timing channels while incurring only 3.4% performance overhead at the RH threshold of 1024.

#### 1 Introduction

Technology scaling has enabled high-capacity DRAMs [66], but also introduced security and reliability challenges such as RowHammer (RH) [44, 49]. To address this, JEDEC recently introduced Per Row Activation Counting (PRAC) in DDR5 [41], which precisely tracks row activations and provides robust RH protection. While PRAC successfully mitigates RH, this paper reveals a new critical security threat: information leakage through timing channels. Our goal is to study the extent of these timing channel risks and to propose a low-cost and secure defense that eliminates them.

The PRAC specification provides robust RH mitigation, even at ultra-low RH thresholds [10, 77, 102]. PRAC achieves this by precisely tracking row activations using its per-row counters and enabling the DRAM to request mitigation time from the memory controller via the Alert Back-Off (ABO) protocol [41]. When a row's activation counter reaches the Back-Off threshold (N<sub>BO</sub>), DRAM asserts the Alert, prompting the memory controller to issue a Refresh Management (RFM) command, termed ABO-RFM, which blocks all memory requests (e.g., for 350ns) to allow RH mitigation. Alternatively, the memory controller may proactively send RFMs when any bank experiences a high number of activations [41]; we Joyce Qu 💿

University of Toronto Department of Computer Science Toronto, ON, Canada joyce.qu@mail.utoronto.ca

#### Prashant J. Nair 💿

The University of British Columbia Department of Electrical and Computer Engineering Vancouver, BC, Canada prashantnair@ece.ubc.ca

call these Activation-Based RFMs (ACB-RFMs). Although effective against RH, we observe that they can inadvertently introduce a new vulnerability-timing channels due to these mitigation actions.

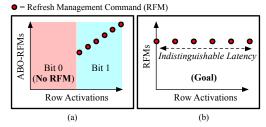

Figure 1(a) shows how high row activations can create timing channels in PRAC-enabled systems. As row activation frequencies increase and consequently more rows surpass  $N_{BO}$ , ABO protocols are triggered more often. This, in turn, leads to an increasing number of ABO-RFMs being issued for mitigation. Each triggered ABO-RFM introduces a 350ns delay at the memory controller, uniformly increasing latency for all concurrent memory accesses to that DRAM channel. These latency variations can be exploited to transmit 'Bit-0' or 'Bit-1' in a cross-core covert channel.

While memory systems have many sources of latency variations, PRAC-based timing channels are uniquely precise, enabling exact values to be reliably transmitted across processes. For instance, a sender can activate a row exactly the  $N_{BO}-X$  times; subsequently, a receiver performing precisely X additional activations on the same row can deterministically trigger an RFM due to ABO protocol (ABO-RFM). We demonstrate that this capability can be exploited to establish both covert and side channels. Thus, our goal is to prevent such timing channels by ensuring RFMs are issued independently of row activations, as shown in Figure 1(b).

This paper observes that all prior RFM-based mitigations–whether PRAC-based [10, 77, 102] or not [35, 47, 78]–issue RFMs based on DRAM row activity. Such *activity-dependent* RFMs can be exploited to create timing channels: in PRAC-based mitigations, attackers can

Figure 1: Timing Channels in PRAC. Alert Back-Off-triggered RFMs (ABO-RFMs) introduce activation-dependent latency, enabling timing channels. An adversary can exploit these to transmit 'Bit-0' or 'Bit-1'. Our goal is to remove this dependency and make RFMs timing independent of activations.

observe a victim's row activation patterns via ABO-RFMs, while in non-PRAC mitigations, they can infer a victim's overall activation levels via Activation-Based RFMs (ACB-RFMs). We focus on timing channels arising from PRAC-based mitigations due to their expected widespread adoption in the near future.

This paper makes two key contributions. First, to demonstrate and analyze the threat posed by PRAC-induced timing channels, we introduce a new class of attacks, *PRACLeak*, which exploits timing variations caused by ABO protocol in PRAC to leak sensitive information. Second, we propose a novel defense, *Timing-Safe PRAC (TPRAC)*, which eliminates these timing channels through a proactive, *activation-independent* mitigation strategy. *TPRAC* is designed to break the link between row activation patterns and memory access latency, effectively neutralizing *PRACLeak* attacks while preserving strong RowHammer protection.

1. The PRACLeak Attacks: Our PRACLeak attacks are built on two key observations. First, PRAC-based mitigations [10, 77, 102] issue RFMs based on DRAM row activation counts. Second, the RFMs triggered by the ABO protocol (ABO-RFM) introduce latency for all concurrent memory accesses, making both their occurrence and associated delays observable system-wide. When an ABO is initiated by the DRAM, the memory controller issues an RFM All Bank (RFM<sub>ab</sub>) command. RFM<sub>ab</sub> halts all memory requests for a predefined period (e.g., 350ns) to allow the DRAM to perform necessary mitigations, increasing the latency of affected memory accesses. This latency impact becomes more pronounced if PRAC is configured to use 2 or 4 RFMs per ABO, extending the delay to 700 or 1400ns. These timing differences can be exploited to form a timing channel for leaking information in both cross-process and cross-VM settings. The only requirement is that the attacker and victim share a memory module. PRACLeak thus enables both covert and side channels, allowing attackers to establish two types of channels:

- Activity-Based Channels: In this channel, the sender and receiver share the same DRAM channel. The sender transmits a single bit of information over a fixed time window by either activating a row beyond N<sub>BO</sub> times (to trigger an ABO-RFM) or not. The receiver monitors the latency of its own memory accesses and decodes the transmitted bit based on the presence ('Bit-1') or absence ('Bit-0') of a latency spike.

- Activation-Count-Based Channels: In this channel, the sender and receiver share a single physical DRAM row. This is feasible if (1) the size of DRAM row (e.g., 8KB) exceeds the physical page size (e.g., 4KB), or (2) the memory controller uses address mapping that spreads data from a single page across multiple DRAM banks to enhance bank-level parallelism, which is common in modern systems [75, 98]. This allows two processes to occupy separate pages within the same row. Here, the receiver can leak the exact activation count of the sender. For example, if N<sub>BO</sub> is 500, and the receiver observes a latency spike after 1 activation, the receiver knows the sender activated that row 499 times. Thus, the sender can transmit any values up to N<sub>BO</sub> (i.e.,  $log_2(N_{BO})$ bits).

Using a PRAC [10] model in Ramulator2 [50, 60], we demonstrate covert channels achieving bitrates of 11–41 Kbps with activitybased channels and 39–124 Kbps with activation-count-based channels in a cross-process setting. We also demonstrate a side-channel attack on an AES T-Table implementation, leaking secret key bits in under 200 encryptions via the activation-count-based channel.

2. TPRAC Mitigation: Timing-Safe PRAC (TPRAC) eliminates PRAC-induced timing channels by replacing activity-dependent mitigations with an activity-independent strategy. It introduces Timing-Based RFMs (TB-RFMs), issued at fixed time intervals and completely independent of row activation behavior. By decoupling RFMs from memory access patterns, TPRAC prevents attackers from inferring activity through latency variations. The time interval between consecutive TB-RFMs (TB-Window) is configured to ensure no DRAM row reaches NBO, even under worst-case attack patterns (e.g., Feinting [61] or Wave [111] attacks). At each TB-RFM, TPRAC proactively mitigates the most heavily activated row-regardless of whether it has reached NBO-using a single-entry mitigation queue per DRAM bank. This preemptive approach eliminates ABO events and the resulting timing channels. TPRAC requires no DRAM modifications and is fully compatible with existing interfaces, making it both secure and practical. For example, at the RH threshold of 1024, issuing one TB-RFM every 1.6 tREFI suffices to close timing channels with just a 3.4% performance slowdown.

#### **Summary of Contributions:**

- Unveiling PRAC Timing Channel Vulnerabilities: To the best of our knowledge, we are the first to reveal the timing channel vulnerability of any RowHammer mitigations. We demonstrate how timing variations introduced by the ABO protocol of PRAC can be exploited to create a new class of timing channels.

- *PRACLeak* Covert-Channel Attacks: Exploiting ABO-induced timing differences, we demonstrate covert-channel attacks achieving 39–124 Kbps when the sender and receiver share a DRAM row, and 11–41 Kbps without requiring shared rows.

- PRACLeak Side-Channel Attacks: Using the same timing channel, we demonstrate a side-channel attack that successfully leaks bits of a secret AES key from a victim running a vulnerable AES T-Table implementation in less than 200 encryptions.

- **TPRAC Defense**: We propose *TPRAC*, a low-cost defense that eliminates PRAC-induced timing channels by proactively issuing RFMs at fixed intervals, independent of row activations. *TPRAC* requires only a single-entry mitigation queue per bank.

#### 2 Background and Motivation

#### 2.1 Threat Model

We consider a realistic threat model where an adversary and a victim share a DRAM module implementing PRAC-based RowHammer (RH) mitigations [10, 77, 102]. The adversary can operate with user-level privileges and run a malicious process to induce Refresh Management (RFM) commands and exploit the resulting timing variations to establish a side or covert channel. By measuring performance metrics such as memory access latency and execution time, the adversary can infer the victim's memory access patterns, enabling them to leak sensitive information (side channel) or transmit secrets (covert channel). We assume that all users can monitor the total number of RFMs within a given time window by issuing memory requests and detecting latency spikes caused by RFMs.

## 2.2 The RowHammer Vulnerability

RowHammer (RH) is a read disturbance issue where rapid activations of DRAM rows (aggressor rows) accelerate charge leakage in neighboring rows (victim rows), leading to bit-flips [44, 49, 76]. The RH has worsened with continued DRAM scaling, as cells become smaller and closely packed. The RowHammer threshold (N<sub>RH</sub>), the minimum number of activations required to induce bit flips, has decreased from 69.2K in 2013 [49] to nearly 4.8K in 2020 [45], and is expected to drop further with future smaller technology nodes.

RH poses a severe security threat and has been exploited in numerous ways [7, 15, 16, 26, 27, 81, 82, 96]. Example attacks include privilege escalation [90], confidential data leakage [53], degradation of ML model accuracy [31, 108], and memory performance attacks (Denial-of-Service) [37, 103]. As N<sub>RH</sub> drops, RH can even occur with benign applications, making it a critical reliability concern [59].

## 2.3 Per Row Activation Counting (PRAC)

The latest DDR5 specification introduces Per Row Activation Counting (PRAC) to address RH [41]. PRAC employs two key mechanisms:

- **Per-Row Activation Counters**: Each DRAM row includes additional activation counter cells and sense amplifiers. On each activation, the corresponding row's counter is incremented; this requires a Read-Modify-Write operation during the precharge phase (i.e., when the row is being closed) [41]. To support this, Relevant DRAM timings (e.g., tRP and tWR) were adjusted in the PRAC specification [41], which we incorporate in our evaluation.

- Alert Back-Off (ABO) Protocol: When a row's counter crosses the Back-Off threshold (N<sub>BO</sub>), the DRAM asserts the Alert signal to request additional mitigation time from the memory controller. In response, the memory controller permits a limited number of additional activations (ABO<sub>ACT</sub>) before initiating the ABO mitigation period. During the mitigation period, the memory controller issues a predefined number of RFM All Bank (RFM<sub>ab</sub>) commands, referred to as the PRAC Level (N<sub>mit</sub>). Each RFM<sub>ab</sub> blocks all memory requests for 350ns (tRFM<sub>ab</sub>), allowing the DRAM to refresh *four* victim rows and *reset* its counter. A subsequent Alert can only be triggered after a specified number of activations (ABO<sub>Delav</sub>), which is set equal to N<sub>mit</sub>.

The PRAC specification also includes proactive Activation-Based RFMs (ACB-RFMs), known as Targeted RFMs, which are triggered when the number of activations of a DRAM bank hits a threshold called the Bank Activation threshold (BAT). BAT is typically set below  $N_{BO}$  (e.g., 75) to reduce or avoid frequent Alerts [41]. Additionally, the specification allows DRAM to perform extra mitigations using the slack time of refresh operations, called Targeted Refresh (TREF), similar to Target Row Refresh (TRR) [30, 40]. As we later show in Section 4.3, TREF can be leveraged to improve the performance of *TPRAC*. Table 1 shows the key PRAC parameters.

Table 1: PRAC Parameters as per JEDEC specification [41]

| Parameter                   | Explanation                                   | Value                                |

|-----------------------------|-----------------------------------------------|--------------------------------------|

| N <sub>mit</sub>            | Num RFMs on Alert (PRAC Level)                | 1, 2, or 4                           |

| ABOACT                      | Max. ACTs to a row from Alert to RFM          | 3 (up to 180ns)                      |

| <b>ABO</b> <sub>Delay</sub> | Min. ACTs after RFM to Alert                  | Same as N <sub>mit</sub> (1,2, or 4) |

| tRFM <sub>ab</sub>          | Duration of RFM All Bank (RFM <sub>ab</sub> ) | 350ns                                |

The PRAC specification provides minimal implementation details to allow DRAM vendors flexibility in their implementations. Consequently, PRAC's security and performance heavily depend on implementation decisions, particularly the design of the mitigation queue. For example, recent studies have shown that PRAC implementations using simple FIFO-based mitigation queues are vulnerable to targeted attacks [77, 102], whereas omitting a mitigation queue entirely can incur severe performance overhead [102]. Therefore, achieving both security and performance in PRAC-enabled systems necessitates careful consideration of the mitigation queue design and its associated management strategy.

#### 2.4 Performance-Driven Timing Channels

A timing channel exploits latency differences to transmit information, serving as a *covert channel* for secret communication or a *side channel* for leaking sensitive data. Performance optimizations in modern systems often create such channels by modulating data access latencies [12, 57, 75, 97]. Mitigation typically involves reducing or disabling these optimizations.

#### 2.5 PRAC: Security-Driven Timing Channel

PRAC-based timing channels are security-driven [41]. Unlike performance-driven timing channels, which can often be mitigated by disabling performance optimizations, disabling PRAC exposes the system to RH attacks. These channels originate from the Alert Back-Off (ABO) protocol: the DRAM asserts the Alert when a row's activation count reaches  $N_{BO}$ . In response, the memory controller issues RFMs for mitigations, and the resulting latency spikes create observable timing variations that can be exploited.

## 2.6 Pitfalls: ABO-RFM and ACB-RFM

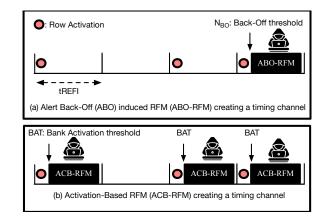

Figure 2 illustrates how PRAC-based RH mitigations [10, 77, 102] rely on *activity-dependent* RFMs, such as ABO-RFM and ACB-RFM.

Figure 2: The activity-dependent nature of PRAC's RFMs allows attackers to exploit them. (a) Repeated activations of a DRAM row up to the Back-Off threshold ( $N_{BO}$ ) trigger an RFM due to ABO (ABO-RFM). (b) Activation-Based RFMs (ACB-RFMs), which mitigate proactively at lower thresholds, can avoid ABO-RFMs but remain exploitable as attackers can still induce ACB-RFMs by activating rows within a bank.

In the case of ABO-RFM (Figure 2(a)), an attacker can repeatedly activate a DRAM row until its activation count reaches  $N_{BO}$ , triggering the ABO protocol. This results in a noticeable latency spike, which can be exploited as a timing channel. In contrast, ACB-RFM is triggered when the total number of activations in a bank crosses BAT, potentially avoiding ABO-RFMs. However, since ACB-RFMs are still tied to activation levels, an adversary can exploit them instead of ABO-RFMs to form timing channels (Figure 2(b)).

## 3 Demonstrating PRAC's Timing Channels

In this section, we demonstrate timing channels inherent in PRAC. While our analysis is based on Understanding PRAC (UPRAC) [8], the presented attacks exploit fundamental features of the PRAC—the Alert Back-Off (ABO) protocol and per-row activation counters—making them applicable to other PRAC-based defenses, including QPRAC [102] and MOAT [77].

We first characterize the timing variations caused by PRAC's ABO protocol (Section 3.1). We then present the proposed *PRACLeak* attacks: first, a covert channel between a spy (receiver) and a trojan (sender) (Section 3.2), followed by a side-channel attack where a spy leaks information from a victim application (Section 3.3).

#### 3.1 Timing Variation due to Alert Back-Off

In PRAC, when any row's activation counter hits the Back-Off threshold ( $N_{BO}$ ), the DRAM asserts the Alert signal to request time for RowHammer (RH) mitigations from the memory controller. In response, the memory controller issues one or more RFM All Bank (RFM<sub>ab</sub>) commands, each stalling all memory requests to the affected channel for tRFM (typically 350ns). As a result, an ABO event introduces a system-wide latency spike, which can be observed by threads running on other cores.

Because ABO occurrences depend on the activation counts of specific physical rows-which can be influenced by an adversarial thread sharing access to these rows-they can leak information about which row was accessed and how frequently it was activated.

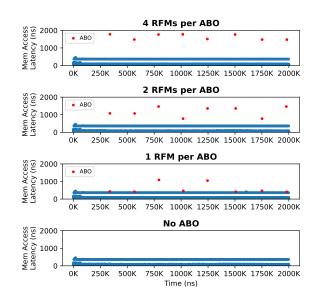

**Characterization.** Figure 3 shows how an adversary can detect an ABO by observing increased memory access latency during its occurrence. We assume the attacker (e.g., a process or VM) monitors its memory access latencies on a different core in the same system as a victim, whose repeated activations trigger an ABO. The attacker accesses a different bank in the same channel and performs repeated accesses–either to the same row in an open-page setting or to different rows in a closed-page setting–to avoid increasing activation counts on its own rows and prevent self-induced ABOs.

Without a concurrent ABO from the victim, the attacker's memory access latency remains relatively stable. However, when the victim's activations trigger an ABO, the attacker experiences a notable increase in its memory accesses latency. The PRAC specification allows for a configuration number of RFMs (1, 2, or 4) per ABO. With 1 RFM per ABO, the attacker observes a latency of 545ns on average. This increases to 976ns and 1669ns with 2 and 4 RFMs, respectively, making the ABO induced by victim activity increasingly detectable.

Figure 3: Timing variation for memory accesses for an attacker in the presence and absence of a concurrent Alert Back-Off (ABO) due to victim's activity.

## 3.2 PRACLeak Covert-Channel Attacks

Covert-channel attacks enable a trojan and a spy to communicate covertly by exploiting shared hardware resources. Our attack leverages the timing impact of the ABO on memory access latency to construct two types of covert channels: (1) an activity-based channel, where a single bit is transmitted based on the presence or absence of an ABO within a fixed time window, and (2) an activation-counterbased channel, where multiple bits are transmitted by encoding information into the timing of an ABO occurrence. We refer to these as the *PRACLeak* Covert-Channel Attacks.

(1) Activity-Based Covert Channel. In this channel, following the strategy described in Section 3.1, the receiver (spy) repeatedly accesses a single memory location in a loop. Under an open-page policy, the receiver flushes the address from the cache to ensure the row-buffer hits. Under a closed-page policy, it accesses addresses mapped to different rows within a bank to prevent activation counters from reaching NBO, thereby avoiding self-induced ABOs. To transmit a 'Bit-1', the sender (trojan) activates a row in a different bank NBO times, typically by alternating accesses to a pair of different rows to cause row-buffer conflicts and guarantee activations. To transmit a 'Bit-0', the sender remains idle, avoiding an ABO. When a 'Bit-1' is transmitted, the ABO triggered by the sender causes a detectable latency spike in the receiver's memory access, while the absence of such a spike indicates a 'Bit-0'. Under a closed-page policy, the transmission period is approximately NBO · tRC + tRFM, reflecting the time required for NBO activations and ABO servicing.

(2) Activation-Count-Based Covert-Channel. A more sophisticated covert channel can be established if the sender and receiver share the same DRAM row. This is possible when the physical page is smaller than the DRAM row, or when successive cache lines are mapped to different banks for bank-level parallelism [75, 98], allowing both parties to access the same DRAM row from different physical pages. In this setup, the sender transmits multiple bits by encoding them into the row's activation counter. For example, within a fixed time window, the sender activates the shared row k times (where  $k < N_{BO}$ ). The receiver then activates the same row up to  $N_{BO}$  times and observes when an ABO-induced delay occurs–specifically, after  $N_{BO} - k$  activations–allowing it to infer the value k. This enables the sender to transmit  $\log(N_{BO})$  bits per time window. Since both the sender and receiver perform up to  $N_{BO}$  activations sequentially, the transmission period is nearly double that of the previous attack: approximately  $2 \cdot N_{BO} \cdot tRC + tRFM$ .

**Results.** We implement these attacks in Ramulator2 [60], a tracebased DRAM simulator, using spy and trojan traces running on different CPU cores. We use the open-sourced UPRAC [8] as our PRAC implementation. While we use PRAC configuration of 4 RFMs per ABO, our bitrates are similar across 1, 2, and 4 RFMs per ABO. Table 2 shows the transmission period (i.e., time for single transmission) and bitrates for our two covert channels, evaluated with N<sub>BO</sub> values ranging from 256 to 1024. At N<sub>BO</sub> of 256, our activity-based covert channel achieves a transmission period of 24.1 $\mu$ s and a bitrate of 41.4Kbps. In contrast, our activation-countbased covert channel has a longer transmission period of 64.7  $\mu$ s. Still, it achieves a higher bitrate of 123.6 Kbps, as it encodes log(N<sub>BO</sub>) bits per period compared to the 1 bit per period in the activitybased channel. As N<sub>BO</sub> increases, bitrates decrease due to longer transmission periods. The error rates are overall negligible (< 0.1%).

**Table 2: Covert Channel Transmission Period and bitrate**

| Туре                   | N <sub>BO</sub> | Transmission<br>Period (μs) | bitrate<br>(Kbps) |

|------------------------|-----------------|-----------------------------|-------------------|

|                        | 256             | 24.1                        | 41.4              |

| Activity-Based         | 512             | 46.7                        | 21.4              |

|                        | 1024            | 91.8                        | 10.9              |

|                        | 256             | 64.7                        | 123.6             |

| Activation-Count-Based | 512             | 128.0                       | 70.3              |

|                        | 1024            | 257.6                       | 38.8              |

#### 3.3 PRACLeak Side-Channel Attacks

This section extends the activation-counter-based covert channel into a side-channel attack. We show how an attacker can infer a victim's memory access patterns-and ultimately leak sensitive information-by observing ABO-induced timing variations. We refer to this as the *PRACLeak* Side-Channel Attack.

**Threat Model.** We assume the attacker and the victim are in different processes or VMs running on different cores of the same system. They share physical DRAM rows, meaning victim secrets are co-located with attacker-controlled data. This can occur either because the DRAM row is larger than a physical page or due to physical-to-DRAM address mappings that stripe successive cache lines across banks for bank-level parallelism, causing data from different processes to map to the same row. The victim is repeatedly executed with attacker-controlled inputs, as in prior attacks [23, 51].

Attack Setup. Crypto libraries like OpenSSL and GnuPG provide an AES implementation with T-tables, known to be vulnerable to

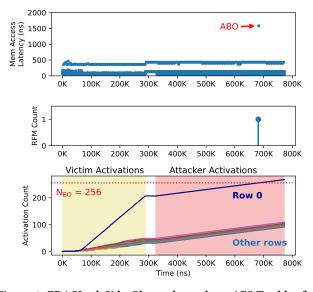

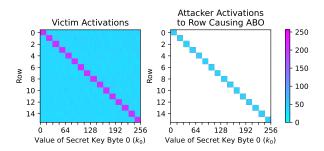

Figure 4: *PRACLeak* Side-Channel attack on AES T-tables for plaintext byte-0,  $p_0 = 0$  with  $k_0 = 0$ . During victim activations, the Row-0 activation counts are approximately double those of the other rows. Thus, the attacker observing the high memory access latency of ABO due to activations on Row-0 learns that it is the most activated row.

cache-based side-channel attacks that leak the secret key [3, 5, 25]. We use this implementation as our target (victim) to demonstrate our ABO-based side-channel attack. Each of the ten rounds in this AES design performs 16 secret-key-dependent memory accesses to 4 T-tables (4 accesses per table). Each table spans 16 cache lines, with each cache line mapped to a different DRAM row. The T-table lookup indices depend on the input plaintext *p* and the secret key *k*. For the first round, they are calculated as  $x_i = p_i \bigoplus k_i$ , where *i* is the byte position in *p* or *k* (*i* goes from 0 to 15).

We perform a chosen plaintext attack on the first AES round. The attacker provides plaintexts to the victim for encryption, keeping  $p_0$  constant while varying other bytes  $p_i$  randomly for  $i \neq 0$ . This ensures that the index  $x_0$  always accesses the same T-table cache line during the first round. The other  $x_i$  (i = 1 to 15) are randomly distributed across all the cache lines. As a result, the cache line corresponding to  $x_0$  has more accesses than the others. Concurrently, the attacker repeatedly evicts these cache lines from all cache levels during the first round-either by flushing them (e.g., using clflush) [109] when the AES library is shared read-only, or by accessing eviction sets for these cache lines in the inclusive LLC [57] or the inclusive coherence directory [107]. For simplicity, we assume the attacker flushes these addresses from the caches in parallel with the victim's execution. Consequently, the DRAM row corresponding to  $x_0$  experiences significantly more memory accesses than the other 15 DRAM rows containing the T-table.

**Attack Mechanism.** The attacker ensures the victim performs *n* encryption iterations with different plaintexts and the same secret key. In each iteration, the attacker ensures the victim accesses T-table entries during the first round. Subsequently, the attacker measures the activation counts of different DRAM rows using the

ABO-based side channel. It sequentially activates each row ( $R_0$ ,  $R_1$ , ...,  $R_{15}$ ) once and repeats this in a loop until one of them triggers an ABO. The first row to trigger an ABO is identified as the most frequently activated row, revealing the cache line number within the T-table that had the highest access count. This discloses 4 of the 8 bits of  $x_0$  (i.e., the cache line index). Since  $p_0$  is known, the attacker recovers 4 of the 8 bits of the key byte  $k_0$ . Repeating this process while fixing each  $p_i$  (*i* going from 0 to 15) allows the attacker to recover 64 out of 128 bits of the secret AES key.

**Results.** Figure 4 shows activation counts for Row-0 and other rows in an attack instance where  $p_0 = 0$  and  $k_0 = 0$ . During the victim execution phase, the victim causes 207 activations to Row-0. In the attacker observation phase, an increase in memory access latency is observed after 49 activations to Row-0 due to an ABO. This is when the combined victim and attacker activations cross N<sub>BO</sub>= 256 for Row-0, the most heavily activated row. From this, the attacker learns the top four bits of  $k_0$ , the first key byte, are 0x0.

Building on this, we generalize our approach to demonstrate that for all secret key bytes  $k_i$ , information can be leaked from the secretdependent most-activated row using our *PRACLeak* side channel. Figure 5(a) shows a heatmap of the number of activations across the 16 DRAM rows containing the T-tables after the victim program runs for 200 encryptions. As  $k_0$  varies from 0 to 256, the DRAM row with the highest number of activations shifts from Row-0 to Row-15. Figure 5(b) then shows the first row that triggers an ABO during the attacker's probing phase, along with its activation count. The total activations to this row-by both victim and attacker-sum to exactly 256, and the row index directly reveals the top 4 bits of key byte  $k_0$ . By varying the fixed plaintext byte  $p_i$ , the attacker can leak 4 of the 8 bits of each  $k_i$ , leaking 50% of the 128-bit AES key.

Figure 5: Side-Channel attack on AES T-tables for varying key byte-0  $k_0$  values, when plaintext byte-0  $p_0 = 0$ . (a) Number of victim activations for DRAM rows after running 200 encryptions. (b) Number of attacker activations on row causing first ABO – index of this row leaks out the key bits.

## 4 Timing-Safe PRAC (TPRAC)

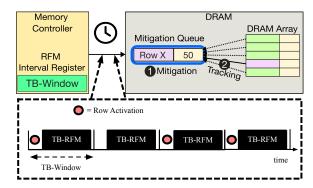

We propose *Timing-Safe PRAC (TPRAC)*, an *activity-independent* Refresh Management (RFM) mechanism that eliminates timing channels in PRAC-based systems. *TPRAC* employs our proposed Timing-Based RFM (TB-RFM), where the memory controller issues RFM All Bank (RFM<sub>ab</sub>) commands at fixed intervals, denoted as TB-Window, independent of memory activity. This closes timing channels while maintaining performance balance.

Figure 6 illustrates how *TPRAC* mitigates PRAC-based timing channels by issuing TB-RFMs periodically at each TB-Window, configured to eliminate Alert Back-Off-triggered RFMs (ABO-RFMs). Section 4.2 discusses how to determine an appropriate TB-Window based on the worst-case attack pattern. *TPRAC* requires only a single register, the RFM Interval Register, to store TB-Window. At the end of each window, it proactively issues an RFM<sub>ab</sub> (as a TB-RFM) regardless of memory activity, preventing attackers from triggering ABO-RFMs through targeted activations. *TPRAC* also disables RFM postponing [41] to prevent attacks that exploit delayed RFMs [61].

Figure 6: Overview of *TPRAC* design. It employs an activityindependent RFM mechanism (Timing-Based RFM) to eliminate timing channels in PRAC-based systems. These RFMs are issued with the fixed time windows called TB-Window.

## 4.1 Underlying PRAC Implementation

Our proposed TB-RFM mechanism relies on the underlying PRAC implementation to perform RowHammer (RH) mitigation during each RFM. However, the PRAC specification [41] does not define implementation details such as the mitigation queue design. Thus, we outline the potential queue designs suitable for *TPRAC*.

*TPRAC* mitigates the most frequently activated row in each DRAM bank during every RFM, similar to prior secure PRAC designs [10, 77, 102]. We propose a frequency-based mitigation queue with a *single-entry* per bank to achieve this practically. Each queue tracks the most highly activated row by storing its address and activation count, replacing the entry when a newly activated row exceeds the current counter ((2) in Figure 6). This ensures that the most activated row is always retained. Upon receiving an RFM, *TPRAC* mitigates the row in each bank's queue, regardless of whether it has crossed the Back-Off threshold (N<sub>BO</sub>) ((1) in Figure 6).

Section 4.2.3 shows that TB-RFM, combined with this queue design, achieves security equivalent to the idealized PRAC design, UPRAC [8]. Similar queue designs are employed in secure PRAC implementations like QPRAC [102] and MOAT [77], making TB-RFM readily compatible with these designs.

#### 4.2 Configuring the TB-Window Interval

To ensure that *TPRAC* effectively eliminates ABO-RFMs–and consequently Activation-Based RFMs (ACB-RFMs)–and prevents information leakage, we must determine an appropriate TB-Window interval for each RowHammer threshold (N<sub>RH</sub>). Our analysis begins with the idealized PRAC implementation, UPRAC [8], which mitigates the most highly activated row in each DRAM bank during every RFM. We then show that *TPRAC* with our proposed singleentry mitigation queue can achieve equivalent security.

4.2.1 Worst-Case Attack Pattern and Assumptions. Following prior studies on RFM [9, 61], we adopt the Feinting [61] (also known as Wave [111]) attack as the basis for our worst-case analysis of *TPRAC*. This attack is mathematically proven to represent the worst-case access pattern for RFM-based mitigations. It proceeds in multiple rounds using a pool of decoy rows and a target row. The decoy rows help bypass RFMs, allowing the attacker to maximize activations on the target row. In each round, all rows in the pool are uniformly activated, and any mitigated rows are removed. This process continues until only the target row remains, enabling the adversary to concentrate all activations on it in the final round. For our security analysis of *TPRAC* under worst-case conditions, we make the following *conservative* assumptions:

- Single ABO-RFM Leakage: The adversary can leak information if even a single ABO-RFM is triggered.

- Exclusive DRAM Access: The adversary has exclusive access to the DRAM module used by the victim, eliminating interference or noise from other processes.

- Full System Knowledge: The adversary knows all details of *TPRAC* and the PRAC implementation, including the Back-Off threshold (N<sub>BO</sub>), mitigation queue design, and TB-Window.

- **Precise Timing Measurement**: The adversary can accurately measure (1) the total number of RFMs, (2) the exact time at which each RFM is issued, and (3) the duration of each RFM-induced blocking period, by monitoring memory access latencies.

4.2.2 Determining TB-Window of TPRAC. The adversary aims to trigger an ABO-RFM by causing  $N_{BO}$  activations to a target row (T<sub>ACT</sub>). To prevent information leakage, *TPRAC* must ensure this count stays below  $N_{BO}$ , as shown in the following equation:

$$T_{ACT} < N_{BO} \tag{1}$$

The adversary begins with an initial pool of  $R_1$  rows. Since *TPRAC* performs one TB-RFM every TB-Window, the maximum number of row activations possible within this interval, denoted as ACT<sub>TB-Window</sub>, is given by:

$$ACT_{TB-Window} = \frac{TB-Window}{tRC}$$

(2)

The number of remaining rows after the first N - 1 attack rounds (R<sub>N</sub>) is computed by subtracting the number of TB-RFMs issued during those rounds from the initial row pool size (R<sub>1</sub>). Since one TB-RFM is issued for every ACT<sub>TB-Window</sub> activations, we have:

$$R_{N} = R_{1} - \left\lfloor \frac{\sum_{i=1}^{N-1} R_{i}}{ACT_{TB-Window}} \right\rfloor, \text{ where } N \ge 2$$

(3)

The total number of attack rounds (AR) can be computed from a given  $R_1$  using Equation (3). Since the target row is activated once per round until the final round, and all activations in the final round (ACT<sub>TB-Window</sub>) go to the target row, the total number of activations to the target row (T<sub>ACT</sub>) is given by:

$$T_{ACT} = (AR - 1) + ACT_{TB-Window}$$

(4)

Lastly, we evaluate the worst-case number of activations to the target row  $(T_{\rm MAX})$  under two scenarios:

• With Activation Counter Reset: Per-row activation counters are reset at every refresh window (tREFW, typically 32ms in DDR5), as proposed in prior work [77]. Original Feinting attack shows that the worst-case occurs when R<sub>1</sub> equals the number of mitigations (i.e., TB-RFMs) that can be applied during the attack [61]. This gives the optimal R<sub>1</sub> value (OPT<sub>R1</sub>) as:

$$OPT_{R_1} = \frac{MAXACT_{tREFW}}{ACT_{TB-Window}}$$

(5)

where MAXACT<sub>tREFW</sub> ( $\sim$ 550K) is the maximum number of activations allowed within one tREFW.

• Without Activation Counter Reset: Per-row activation counters are reset only when the row is mitigated via an RFM. In this case, we sweep  $R_1$  from 1 up to its maximum possible value (128K for the DDR5 32Gb chip) to determine the value of  $OPT_{R_1}$  that maximizes the number of activations to the target row.

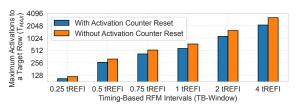

Figure 7 shows the theoretical maximum number of activations to the target row (T<sub>MAX</sub>) across different TB-Window values, comparing scenarios with and without per-row activation counter reset at each tREFW. T<sub>MAX</sub> is consistently higher without counter reset due to the larger optimal initial row pool size  $(OPT_{R_1})$ . With counter reset, OPT<sub>R1</sub> is constrained by how many TB-RFM intervals fit within a single tREFW window. For example, at TB-Window of 1 tREFI, only 8192 intervals are possible, limiting OPT<sub>R1</sub> to 8192almost 16× smaller than the no-reset case (approximately 128K). As a result, T<sub>MAX</sub> reaches 736 without counter reset, compared to 572 with reset. The impact of the reset becomes more pronounced at longer TB-Window intervals because fewer TB-RFMs fit within tREFW, further reducing  $OPT_{R_1}$ . For instance, at TB-Window of 4 tREFI,  $T_{MAX}$  reaches 3220 without reset and 2138 with reset. Conversely, at shorter intervals like 0.25 tREFI, the difference narrows, with T<sub>MAX</sub> values of 118 and 105, respectively.

Figure 7: Theoretical maximum activations to a target row  $(T_{MAX})$  as the TB-Window of *TPRAC* varies, shown for both with and without per-row activation counter reset at each refresh window (tREFW). Results are based on a DDR5 32Gb chip with 128K rows per bank.  $T_{MAX}$  must remain below the Back-Off threshold (N<sub>BO</sub>) to avoid Alert Back-Off-triggered RFMs (ABO-RFMs) and close timing channels.

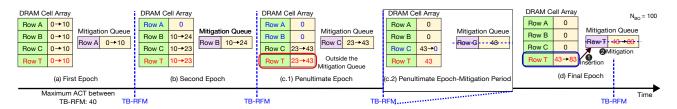

4.2.3 Impact of the Mitigation Queue Structure of PRAC. We demonstrate that a single-entry, frequency-based mitigation queue is sufficient to match the security guarantees of UPRAC. Figure 8 illustrates through a simple Feinting attack, where the attacker uses three decoy rows alongside a target row (Row T) to bypass TB-RFMs and build up activations on Row T. In this example, up to 40 activations are allowed within each TB-Window. During the first epoch, all four rows are activated uniformly, as shown by Figure 8(a). Row

Figure 8: Example of how TPRAC prevents Feinting [61] or Wave [111] attack with a single-entry mitigation queue.

A, having the highest activation count, is tracked in the mitigation queue and then mitigated when the TB-RFM is issued. In the second epoch, the attacker continues activating Row T and the remaining decoys. Row B accumulates the most activations and is tracked and mitigated at the next TB-RFM, as shown by Figure 8(b).

**Final Attack Round:** At the end of the penultimate epoch (Figure 8(c.1)), both the target row (Row T) and a decoy row (Row C) have equal activation counts (i.e., 43). Since the mitigation queue holds only a single entry, only one row–Row C–is tracked and subsequently mitigated when the TB-RFM is issued, as shown by Figure 8(c.2). During this mitigation period, memory requests are blocked for 350ns, preventing the attacker from issuing further activations, including to Row T. In the final round (Figure 8(d)), the attacker focuses activations solely on Row T. As soon as Row T is activated, Row T becomes the most active row and is inserted into the mitigation queue (1) in Figure 8). Before it reaches the Back-Off threshold (N<sub>BO</sub> = 100 in this example), the next TB-RFM is issued, and Row T is mitigated (2) in Figure 8), ensuring no ABO-RFM is triggered, consistent with our analysis in Section 4.2.

Notably, if the attacker had begun targeting Row T earlier, it would have entered the mitigation queue and been mitigated sooner, further reducing the attack's effectiveness. This behavior aligns with observations from the original Feinting attack [61].

**Scenario 1 – Equal Activations:** In this scenario, the attacker uniformly activates all rows in the initial pool across rounds, including rows that were mitigated in previous epochs. However, this strategy is suboptimal compared to the Feinting attack. Once a row is mitigated, its counter resets to zero (e.g., Row C in Figure 8(c.2)), so continuing to activate it reduces the total activations available for the target row. For instance, if both Row C and Row T are activated in Figure 8(d) rather than focusing solely on Row T, the target row receives only 20 activations instead of 40. This observation aligns with the findings from the original Feinting attack [61].

**Scenario 2 – Delayed Activations:** In this scenario, the attacker first activates decoy rows (e.g., Row B and Row C) to inflate their activation counts, ensuring they are mitigated when TB-RFMs are issued. The attacker then switches to intensively activating the target row (Row T) so it becomes the most activated and enters the mitigation queue. If the same row pool size, number of decoy rows, and activation counts are used, this strategy effectively replicates the Feinting attack. However, it does not improve Feinting's effectiveness and remains secure under *TPRAC*.

**Scenario 3 – Early and Aggressive Activations:** In this scenario, the attacker begins by aggressively activating the target row (Row T), aiming to reach the Back-Off threshold (N<sub>BO</sub>) before any mitigations occur. Row T quickly surpasses other rows in activation count

and enters the mitigation queue. However, this strategy is inferior to the Feinting attack. Once Row T is mitigated by a TB-RFM, its counter resets, limiting the total number of activations to those between two TB-RFM events; this number is significantly lower than what the Feinting attack can achieve. For example, with one TB-RFM every tREFI, the attacker can induce at most 60 activations–approximately 12.3× and 9.5× fewer than the maximum derived in our analysis without (736) and with (572) counter reset, respectively (Figure 7).

Why a Single-Entry Queue is Sufficient: A single-entry, frequency-based mitigation queue is sufficient because it consistently tracks the most frequently activated row at any point in time, ensuring that the highest-risk row is mitigated during each TB-RFM. Since TB-RFMs are issued at fixed intervals, *independent* of memory access patterns, the attacker cannot manipulate mitigation timing through activation strategies. As a result, no row can accumulate enough activations to reach N<sub>BO</sub>, effectively preventing all ABO-RFMs. Therefore, by combining a single-entry queue with appropriately configured TB-RFMs, *TPRAC* achieves security on par with idealized PRAC implementations (UPRAC). This design effectively thwarts a wide range of attack strategies, including balanced, delayed, and aggressive activations, ensuring robust protection even against worst-case patterns like the Feinting attack.

## 4.3 Designing TPRAC with Targeted Refreshes

*TPRAC* can leverage existing Targeted Refreshes (TREFs) to reduce mitigation overhead. Like TB-RFMs, each TREF is used to mitigate the most frequently activated row from the mitigation queue. This allows *TPRAC* to skip a scheduled TB-RFM if a TREF occurs within the same interval, improving performance without sacrificing security. For example, at N<sub>RH</sub> of 512, *TPRAC* requires a TB-RFM approximately every 0.8 tREFI with counter reset, and every 0.6 tREFI without reset, to eliminate timing channels (Figure 7). If TREFs are issued once every 2 tREFI, *TPRAC* can skip a TB-RFM roughly every 2.5 tREFI (with reset) or 3.3 tREFI (without reset), reducing the total number of RFMs and improving performance.

## 5 Evaluation Methodology

**Simulation Framework:** We evaluate our design using Champ-Sim [24], a well-known trace-based, out-of-order processor simulator. We integrate ChampSim with the cycle-accurate DRAM simulator Ramulator2 [50, 60]. Table 3 summarizes our simulated system configuration, following prior work [71] that models the Intel Sunny Cove microarchitecture.

The baseline system features a 4-core out-of-order processor with a hashed perceptron branch predictor [42]. Each core has

private L1 caches: a 32KB instruction cache and a 48KB data cache, with the data cache using the IP-stride prefetcher [13]. Each core also has a private 512KB L2 cache, and all cores share an 8MB last-level cache (LLC). The LLC supports 64 MSRHs per core and uses the SPP-PPF prefetcher [4] and SRRIP replacement policy [36]<sup>1</sup>. The memory system comprises a single-channel, quad-rank DDR5 memory totaling 128GB of DRAM. The memory controller uses the Minimalist Open-Page (MOP) address mapping policy [43] and the First Ready First Come First Served (FR-FCFS) scheduler [83, 116], following prior work [9, 10, 102, 103]. The DDR5 memory is modeled as a 32Gb DDR5-8000B chip, with timing parameters and PRAC-specific adjustments based on the JEDEC specification [41].

| Out-Of-Order Cores                       | 4 Cores, 4GHz, 6-issue width, 4-retire width<br>352-entry ROB, hashed perceptron branch predictor [42] |

|------------------------------------------|--------------------------------------------------------------------------------------------------------|

| L1 Instruction Cache                     | 32KB, 8-way, 4 cycles                                                                                  |

| L1 Data Cache                            | 48KB, 12-way, 5 cycles, IP-stride prefetcher [13]                                                      |

| L2 Cache                                 | 512KB, 8-way, 10 cycles                                                                                |

| Last Level Cache (Shared)                | 8MB, 16-way, 20 cycles, SPP-PPF prefetcher [4], SRRIP [36]                                             |

| Address Mapping                          | Minimalist Open-Page (MOP) [43]                                                                        |

| Scheduling Policy                        | FR-FCFS [83, 116] with a cap of 4 [63]                                                                 |

| Memory Type                              | 32Gb DDR5-8000B                                                                                        |

| DRAM Organization                        | 4 Bank x 8 Groups x 4 Ranks x 1 Channel                                                                |

| Rows Per Bank, Size                      | 128K, 8KB                                                                                              |

| tRCD, tCL, tRAS [11]                     | 16ns, 16ns, 16ns                                                                                       |

| tRP, tRTP, tWR, tRC                      | 36ns, 5ns, 10ns, 52ns                                                                                  |

| tRFC, tREFI [64, 80]                     | 410 ns, 3.9µs                                                                                          |

| tABO <sub>ACT</sub> , tRFM <sub>ab</sub> | 180ns, 350ns                                                                                           |

Evaluated Design: We evaluate the performance and energy impact of TPRAC by comparing it to a baseline PRAC-enabled DRAM without the Alert Back-Off (ABO) protocol. We extend Ramulator2 to model per-row activation counters, the ABO protocol, our proposed Timing-Based RFM (TB-RFM), and the mitigation queue design and strategy. The TB-RFM interval (TB-Window) is tuned for each RowHammer (RH) threshold (NRH) to eliminate all ABOtriggered RFMs (ABO-RFMs). We compare TPRAC against the following baselines, which are insecure against timing channel attacks. As the underlying PRAC implementation, we use QPRAC [102], one of the existing secure PRAC designs [10, 77, 102]: 1) ABO-Only, which relies solely on the ABO protocol for RH mitigations, and 2) ABO+ACB-RFM, which incorporates proactive Activation-Based RFMs (ACB-RFMs) to eliminate ABO-RFMs, which is the current RFM implementation defined in the JEDEC standard [41]. For each N<sub>RH</sub>, we configure the Bank Activation threshold (BAT) to eliminate ABO-RFMs under the worst-case Feinting [61] (or Wave [111]) attack pattern.

**Workloads:** We evaluate 50 publicly available workloads from SPEC2006 [17], SPEC2017 [95], and CloudSuite [21] benchmarks. Workloads are categorized into three memory-intensity groups based on their row-buffer misses per kilo instructions (RBMPKI): High (H) for RBMPKI  $\geq$  10, Medium (M) for 1  $\leq$  RBMPKI < 10, and Low (L) for RBMPKI < 1, as shown in Table 4.

| Table 4: | Worklo | ad Categ | orization | Based of | on RBMPKI |

|----------|--------|----------|-----------|----------|-----------|

|          |        |          |           |          |           |

| RBMPKI            | Workloads                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| High<br>[10+)     | nutch, cassandra, classification, 433.milc, cloud9,<br>410.bwaves, 470.lbm, 471.omnetpp, 483.xalancbmk,<br>519.lbm, 520.omnetpp, 649.fotonik3d, 450.soplex, 619.lbm,<br>429.mcf, 654.roms, 470.lbm, 483.xalancbmk, 471.omnetpp,<br>605.mcf, 482.sphinx3, 437.leslie3d, 627.cam4, 620.omnetpp,<br>628.pop2, 607.cactuBSSN, 436.cactusADM, 459.GemsFDTD |  |  |

| Medium<br>[1, 10) | 401.bzip2, 657.xz, 602.gcc, 473.astar,<br>623.xalancbmk, 464.h264ref, 481.wrf                                                                                                                                                                                                                                                                         |  |  |

| Low<br>[0, 1)     | 631.deepsjeng, 458.sjeng, 456.hmmer, 625.x264, 403.gcc,<br>444.namd, 603.bwaves, 456.hmmer, 464.h264ref,<br>638.imagick, 644.nab, 481.wrf, 600.perlbench, 621.wrf,<br>465.tonto, 447.dealII, 435.gromacs, 641.leela, 454.calculix,<br>445.gobmk, 453.povray, 416.gamess, 648.exchange2                                                                |  |  |

We simulate four-core homogeneous workloads for SPEC2006 and SPEC2017, while each core in CloudSuite runs a distinct thread per workload. For SPEC workloads, each core executes 250 million instructions, comprising a 50M warm-up followed by 200M instructions used for performance measurement. For CloudSuite, each core executes 25M warm-up followed by 125M measured instructions.

By default, we set  $N_{RH}$  to 1024 with one RFM per Alert (PRAC-1) and enable activation counter resets at every tREFW. Additionally, we analyze sensitivity to  $N_{RH}$  values from 128 to 4096, PRAC levels with 1, 2, or 4 RFMs per Alert, targeted refresh rates varying from once every 1 to 4 tREFIs, and activation counter reset policies. Performance is measured using weighted speedup.

## 6 Results and Analysis

## 6.1 Empirical Security Validation

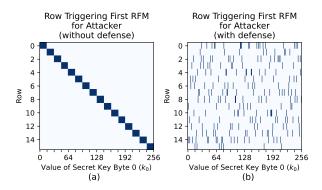

To empirically demonstrate the effectiveness of TPRAC's mitigation capability, Figure 9 shows the results of the *PRACLeak* Side-Channel attack on AES T-tables (described in Section 3.3), both with and without our *TPRAC* defense. The figure shows that the DRAM row that triggers the first RFM during the attacker's probing phase

Figure 9: Row triggering the first RFM for the attacker. Without our *TPRAC* defense, the row leaks the secret key value, whereas with the defense, the triggered row is random and does not reveal any secret information.

<sup>&</sup>lt;sup>1</sup>We evaluated *TPRAC* with various branch predictor and prefetcher combinations in ChampSim. The result variance is within 1%, showing that our mitigation is insensitive to different microarchitectural policies.

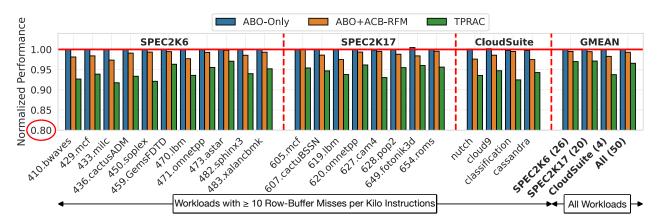

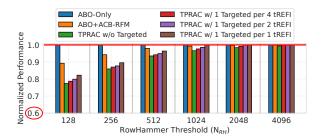

Figure 10: Normalized performance of *TPRAC* compared to insecure baselines, ABO-Only and ABO+ACB-RFM, at a RowHammer threshold of 1024. *TPRAC* incurs a slowdown of only 3.4% on average due to periodic Timing-Based RFMs (TB-RFMs). In contrast, ABO+ACB-RFM and ABO-Only exhibit slowdowns of 0.7% and near zero, respectively, due to their lower RFM frequency resulting from their activity-dependent design. However, this activity-dependent RFM method is not secure.

reveals the most heavily activated row during the victim execution, which is dependent on the secret key.

In Figure 9(a), without the defense, there is a strong correlation between the value of key byte  $k_0$  and the row triggering the first RFM, clearly leaking  $k_0$ . In contrast, Figure 9(b) shows that with *TPRAC*, the row triggering the first RFM appears random, leaking no information to the attacker. This is due to two reasons: (1) *TPRAC*'s periodic Timing-Based RFMs (TB-RFMs) proactively mitigate the most activated rows, fully preventing ABO-RFMs; and (2) even if the TB-RFM interval (TB-Window) is misconfigured, the attacker cannot distinguish TB-RFMs from ABO-RFMs, as both incur the same 350ns latency. As a result, no secret information is leaked through memory latency variations.

#### 6.2 Performance Overhead

Figure 10 shows the performance of *TPRAC* at a RowHammer threshold (N<sub>RH</sub>) of 1024, compared to two insecure baselines: ABO-Only and ABO+ACB-RFM. Performance is normalized to a PRAC-enabled DDR5 system without the ABO protocol. *TPRAC* incurs only a 3.4% average slowdown, as issuing one Timing-Based RFM (TB-RFM) every 1.6 tREFI (6.2µs) is sufficient to eliminate all ABO-RFMs. The primary source of overhead is reduced DRAM bandwidth-each TB-RFM block all banks for 350ns (tRFM<sub>ab</sub>) every 6.2µs, leading to a maximum DRAM bandwidth loss of 5.6%  $\left(\frac{\text{tRFM}_{ab}}{\text{TB-Window}}\right)$ . As a result, several memory-intensive workloads experience slowdowns near or slightly above 6%.

Another source of slowdown is reduced row-buffer locality. Since each TB-RFM requires closing all open rows to issue an RFM<sub>ab</sub>, row-buffer hit rates may decline. On average, *TPRAC* increases row-buffer misses by only 0.5%, with negligible impact on most workloads. However, in *433.milc*, a 2.3% increase in misses, combined with bandwidth loss, results in the highest slowdown of 8.3%.

ABO+ACB-RFM incurs only a 0.7% slowdown, as it triggers Activation-Based RFMs (ACB-RFMs) only when per-bank activations reach the Bank Activation threshold (BAT), minimizing the bandwidth loss. ABO-Only shows almost no slowdown because ABO-RFMs are rare at  $N_{RH}$  of 1024. These results are consistent with recent works [10, 77, 102]. However, both ABO-Only and AB-O+ACB-RFM remain vulnerable to timing channel attacks due to their *activity-dependent* mitigation strategies.

#### 6.3 Sensitivity to PRAC Levels

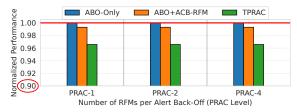

Figure 11 compares the performance of *TPRAC* and insecure baselines, ABO-Only and ABO+ACT-RFM, as the PRAC level–the number of RFMs per ABO–varies at N<sub>RH</sub> of 1024. While higher PRAC level allows DRAM to mitigate more rows per ABO, they also increase DRAM blocking time, which can impact both performance and security when ABO-RFM occurs. The results show that PRAC level variation has no impact on the performance of *TPRAC* and ABO+ACB-RFM, since both designs eliminate all ABO-RFMs. *TPRA-C* achieves this through periodic Timing-Based RFMs (TB-RFMs), while ABO+ACB-RFM uses Activation-Based RFMs (ACB-RFMs). Across all PRAC levels, *TPRAC* and ABO+ACB-RFM incur slowdowns of 3.4% and 0.7%, respectively. ABO-Only experiences almost no ABO-RFMs at this threshold, resulting in near-zero slowdown.

Figure 11: Performance comparison of *TPRAC* and insecure baselines, ABO-Only and ABO+ACB-RFM, across different PRAC levels at a RowHammer threshold of 1024. Performance remains consistent across PRAC levels. *TPRAC* and ABO+ACB-RFM incur slowdowns of 3.4% and 0.7%, respectively, due to proactive RFMs reducing DRAM bandwidth. In contrast, ABO-Only shows almost no overhead, as ABO-RFMs are rare in benign applications at this threshold.

## 6.4 Sensitivity to Targeted Refreshes

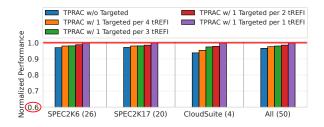

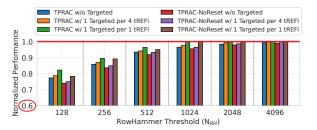

Figure 12 shows the performance of *TPRAC* as the frequency of Targeted Refreshes (TREFs) varies from once every four tREFI to once per tREFI at a RowHammer threshold (N<sub>RH</sub>) of 1024. Increasing TREF frequency improves performance since it allows *TPRAC* to skip more Timing-Based RFMs (TB-RFMs). Without TREF, *TPRAC* incurs a 3.4% slowdown. The slowdown drops to 2.4%, 2.0%, and 1.4% with one TREF every 4, 3, and 2 tREFIs, respectively. At one TREF per tREFI, *TPRAC* incurs no slowdown, as TREFs fully replace TB-RFMs, eliminating ABO-RFMs and preventing timing channels. As discussed in Section 6.5, this approach enhances the practicality of *TPRAC* at lower N<sub>RH</sub> by reducing performance slowdowns.

Figure 12: Normalized performance of *TPRAC* as the frequency of Targeted Refreshes (TREFs) varies at  $N_{RH}$  of 1024. More frequent TREFs reduce slowdowns by reducing the need for Timing-Based RFMs. *TPRAC* incurs slowdowns of 3.4%, 2.4%, 2.0%, and 1.4% with one TREF per 4, 3, and 2 tREFI, respectively, and no overhead with one TREF per tREFI.

#### 6.5 Sensitivity to RowHammer Threshold

Figure 13 shows the performance of *TPRAC* as  $N_{RH}$  varies from 128 to 4096. At  $N_{RH}$  of 4096, 2048, and 1024, *TPRAC* incurs slowdowns of 0.6%, 1.6%, and 3.4%, respectively. Even at an ultra-low  $N_{RH}$  of 512, it maintains a moderate overhead of 6.5%. However, with lower  $N_{RH}$  of 256 and 128, the slowdown rises to 14.1% and 22.6%,

Figure 13: Performance comparison of *TPRAC* and insecure baselines, ABO-Only and ABO+ACB-RFM, as  $N_{RH}$  varies. *TPRAC* incurs 3.4%, 1.6%, and 0.6% slowdown at  $N_{RH}$  of 1024, 2048, and 4096, respectively. However, slowdowns increase to 6.5%, 14.1%, and 22.6% for  $N_{RH}$  of 512, 256, and 128, respectively, due to more frequent Timing-Based RFMs (TB-RFMs). Co-designing *TPRAC* with Targeted Refreshes improves performance by allowing some TB-RFMs to be skipped.

respectively, due to  $4.3 \times$  and  $6.4 \times$  more frequent TB-RFMs needed to eliminate ABO-RFMs and prevent timing channel attacks.

Co-designing *TPRAC* with Targeted Refreshes (TREFs) improves performance across all evaluated  $N_{\rm RH}$  values, as it can skip some TB-RFMs by leveraging TREFs. At  $N_{\rm RH}$  of 256, this reduce the slowdown from 14.1% (Without TREF) to 13.0%, 12.3%, and 10.5% with one TREF every 4, 2, and 1 TREF, respectively.

ABO+ACB-RFM shows similar trends, with slowdowns increasing at lower N<sub>RH</sub> due to more frequent ACB-RFMs issued to eliminate ABO-RFMs. Its overhead remains lower than *TPRAC*, incurring just 0.7% at N<sub>RH</sub> of 1024 and 10.7% at 128. However, it remains vulnerable to timing channel attacks, and the vulnerability worsens as N<sub>RH</sub> decreases because more frequent ACB-RFMs increase the chance of information leakage. ABO-Only incurs negligible slowdowns across all thresholds, since ABO-RFMs are rare in benign applications. Nonetheless, like ABO+ACB-RFM, it is insecure against timing channels, with leakage becoming more pronounced at lower N<sub>RH</sub>, where fewer activations are needed to trigger ABO-RFMs.

#### 6.6 Sensitivity to Activation Counter Reset

Figure 14 shows the performance of *TPRAC* with and without activation counter reset as N<sub>RH</sub> varies from 128 to 4096. At N<sub>RH</sub> of 1024 and above, the impact of counter reset is negligible, with performance differences under 1%. However, at ultra-low N<sub>RH</sub> (N<sub>RH</sub>  $\leq$  512), resetting counters every tREFW improves performance. For instance, at N<sub>RH</sub> of 128 without TREF, *TPRAC* without counter reset incurs a 73.9% slowdown, compared to 77.4% with reset, resulting in a 3.4% performance improvement. This improvement arises from a lower TB-RFM frequency, as counter resets reduce the attacker's initial row pool size (see Section 4.2). With fewer TB-RFMs, DRAM suffers less bandwidth loss, resulting in better overall performance.

Figure 14: Normalized performance of *TPRAC* with and without activation counter reset as N<sub>RH</sub> varies from 128 to 4096. Resetting counters at each tREFW has negligible impact (< 1%) at N<sub>RH</sub>  $\geq$  1024, but offers noticeable performance benefits at lower thresholds due to reduced TB-RFM frequency.

#### 6.7 Energy Overhead

Table 5 presents the energy overhead of *TPRAC*. Our TB-RFM introduces two main sources of overhead. First, each TB-RFM triggers mitigations for the most heavily activated row in the mitigation queue, consisting of *four* victim refreshes and *one* aggressor activation to reset the counter, totaling *five* additional activations per TB-RFM. Second, TB-RFMs increase overall execution time, contributing to what we refer to as non-mitigation energy overhead. At N<sub>RH</sub> of 1024, *TPRAC* incurs an average energy overhead of 7.4%, primarily due to increased execution time. As N<sub>RH</sub> decreases, more frequent TB-RFMs are required, increasing the overhead. For example, at N<sub>RH</sub> of 4096, TB-RFMs are issued approximately once every seven TREF, leading to only 1% overhead. In contrast, at ultralow N<sub>RH</sub> of 128, TB-RFMs are issued every 1 $\mu$ s-nearly 29× more often-resulting in significant 44.3% overhead.

Notably, the JEDEC DDR5 specification defines the minimum Bank Activation threshold (BAT) for ACB-RFM as 16 [41], which allows issuing one ACB-RFM every  $0.8\mu$ s. This rate is similar to the  $1\mu$ s TB-RFM interval at N<sub>RH</sub> of 128. As a result, the worst-case energy overhead of *TPRAC* aligns with what is already permissible in the standard. Future work can explore *TPRAC* to reduce energy impact at ultra-low N<sub>RH</sub>.

Table 5: Energy Overhead of TPRAC

| N <sub>RH</sub> | Mitigation<br>(RFM) | Non-Mitigation<br>(Execution Time) | Total |

|-----------------|---------------------|------------------------------------|-------|

| 128             | 18.1%               | 26.2%                              | 44.3% |

| 256             | 11.3%               | 14.8%                              | 26.1% |

| 512             | 5.9%                | 4.5%                               | 10.4% |

| 1024            | 2%                  | 5.4%                               | 7.4%  |

| 2048            | 1%                  | 1.6%                               | 2.6%  |

| 4096            | 0.45%               | 0.55%                              | 1%    |

#### 6.8 Storage Overhead

*TPRAC* introduces minimal storage overhead by requiring only a single register per memory controller to store the interval for issuing periodic Timing-Based RFMs (TB-RFMs). This RFM interval register uses 24 bits (3 bytes), which is sufficient to represent intervals up to approximately half of the tREFW duration.

## 7 Alternative Timing Channel Mitigations

#### 7.1 Obfuscation-Based Defenses

An alternative to mitigating PRAC-induced timing channels is to obfuscate the attacker by injecting random noise into memory access latency. The key idea is to introduce timing delays that resemble legitimate ABO-RFMs (350ns), making it harder for attackers to infer sensitive information. This can be achieved by having either the memory controller issue random RFM<sub>ab</sub>s or the DRAM probabilistically assert the Alert signals. While this approach does not eliminate ABO-RFMs like *TPRAC*, it is effective against simple channels that rely solely on memory access latency variations.

An attacker could develop more sophisticated strategies beyond simple latency monitoring. For example, they might profile RFM count distributions over extended periods (e.g., hours or days), collecting data from windows with and without memory activity. The attacker could attempt to infer transmitted bits or secret-dependent behavior by training statistical or machine learning classifiers on this data. If random RFMs are injected with 50% probability per tREFI, the attacker may typically observe around 4096 RFMs within a tREFW window during idle periods and higher counts during active ones. In extreme cases, observing zero RFMs can definitively indicate a Bit-0 (covert channel) or absence of victim activity (side channel), while counts exceeding 8192 confirm a Bit-1 or victim activity. Nonetheless, the distribution overlap introduced by randomization reduces the reliability of such inferences.

This probabilistic approach offers a flexible trade-off between security and performance. While it does not eliminate all information leakage, it reduces attacker precision, making it suitable in scenarios where occasional leakage is acceptable. It is also appealing for ultralow  $N_{RH}$  values, where *TPRAC* incurs higher performance overhead due to frequent TB-RFMs. Future work will further explore how such techniques can complement or enhance *TPRAC*.

## 7.2 Bank Partitioning with Per-Bank RFM

DRAM bank partitioning, where each bank is exclusively assigned to a specific user or process (e.g., per-VM), can provide spatial isolation and prevent inter-bank interference [58, 92]. While this can block some PRAC-based timing channels, such as our activationcount-based channel, it is insufficient to prevent all channels, including our activity-based channel. This is because the PRAC specification only allows memory controllers to issue an RFM All Bank (RFM<sub>ab</sub>), which blocks the entire DRAM channel for 350ns [41]. Consequently, an attacker in a separate bank on the same DRAM module can still observe latency spikes and infer victim activity.

One way to close these timing channels under bank partitioning is to extend the ABO protocol to support a fine-grained Per-Bank RFM (RFM<sub>pb</sub>) command, which mitigates a specific bank without stalling others. However, this requires changes to the current PRAC specification, such as enabling DRAM to report to the memory controller which bank triggered the Alert signal. In contrast, *TPRAC* eliminates all PRAC-induced timing channels without requiring such modifications or bank partitioning.

$\rm RFM_{pb}$  could also benefit *TPRAC* by allowing it to issue Per-Bank TB-RFM, further reducing DRAM bandwidth loss. We leave the design and evaluation of this extension to future work<sup>2</sup>.

## 7.3 Hiding RFM-Induced Latency Variations

Another approach to mitigating PRAC's timing channels is to hide or eliminate the observable latency of RowHammer (RH) mitigation caused by Alert Back-Off-triggered RFMs (ABO-RFMs). For instance, this can be done by increasing the frequency of periodic retention refreshes and borrowing time from them to perform necessary mitigations, similar to prior Target Row Refresh (TRR). Instead of issuing *TPRAC*'s Timing-Based RFMs (TB-RFMs), this method uses additional refreshes to track and mitigate the most frequently activated rows using an in-DRAM mitigation queue and mitigate them, following a mitigation strategy of *TPRAC*.

However, this approach has key limitations: (1) it requires changes to JEDEC specifications, (2) incurs higher performance overhead due to longer blocking time (410ns for Refresh vs. 350ns for RFM), (3) must be conservatively configured for worst-case N<sub>RH</sub> due to aging and spatial variation [72, 112], and (4) complicates DRAM refresh logic by repurposing refreshes for both retention and RH mitigation. In contrast, *TPRAC* uses JEDEC-defined RFM commands, offering a more efficient and standards-compliant solution.

$<sup>^2</sup>$ QPRAC [102] also proposes to incorporate RFM<sub>pb</sub> as part of the ABO protocol to address Denial-of-Service risks. In contrast, our focus is on closing timing channels.

#### 8 Related Work

#### 8.1 Timing Side Channels

**DRAM Timing Channels.** DRAMA [75] proposes a side channel due to timing variation between row-buffer hits and conflicts. While this leaks the last row or bank accessed, our PRAC-based attacks can leak the history of row accesses, leaking the activation counts for any row accessed in a given time window.

Other works [18, 92, 99, 100, 115] discuss side channels due to memory-scheduling decisions in shared memory controllers, and propose spatial [92, 100] or temporal partitioning [99], or memory traffic shaping [18, 115] to prevent leakage. Such defenses cannot mitigate all PRAC-based timing channels, as the RFM<sub>ab</sub> command used for mitigation in PRAC stalls the entire DRAM channel, causing delays for all memory accesses despite such defenses. Our solution, TPRAC, closes all PRAC-based timing channels.

Security-Metadata based Timing Channels. Security metadata can introduce timing side channels. MetaLeak [14] showed that Intel SGX's Merkle trees leak timing information. For instance, victim accesses trigger tree traversals that slow an attacker's traversals. Similarly, split counters [84, 85, 106] expose a victim's access counts via shared counter cache lines and overflow behavior. Our attacks also leverage activity-based and counter-based channels, but target PRAC-based row-activation counters. Unlike integrity trees and counter-based encryption [114], which are now obsolete in new variants of SGX (SGX-v2) [33], PRAC is added to the DDR5 DRAM specification and is likely to be widely adopted. Thus, our attacks are more widely applicable.

**Timing Channels Due to Performance Optimizations.** Most timing channels are due to timing variations introduced by performance optimizations. Among these, cache timing channels [3, 28, 57, 109] have been the most well-explored, with the root cause being timing variations due to cache hits and misses. Recently, cache performance optimizations like prefetchers [12, 93, 97] and way-predictors [55] have also been shown to cause timing variations and side channels. Moreover, processor front-end optimizations like branch prediction [19] and speculative execution [51, 56], critical for performance, have also been shown to be vulnerable to side channels. Unlike these side channels, which can be mitigated by disabling performance optimizations for sensitive computations (e.g., using fences or uncached memory), our PRAC-based side channels cannot be mitigated by disabling activation counters, as that can lead to vulnerability to RowHammer.

## 8.2 Alternative RowHammer Defenses

**A. TRR-Based Defenses:** TRR-based defenses mitigate RowHammer (RH) by borrowing time from periodic refreshes to perform mitigation, either probabilistically [32, 48] or based on counters tracking frequently activated rows [30]. While these approaches avoid additional latency and are generally immune to timing channels, they have been shown to be ineffective against modern RH attacks [22, 30, 34, 38, 39, 52]. In contrast, *TPRAC* remains secure against RH attacks while also eliminating timing channels.

**B. RFM-Based In-DRAM Defenses:** These in-DRAM defenses perform RH mitigations using Activation-Based RFMs (ACB-RFMs).

Upon receiving an RFM, some approaches apply mitigation probabilistically [35, 78], while others use tracking structures to determine which rows to mitigate [47, 61]. Although effective against RH, these techniques are vulnerable to timing channels because they rely on activity-dependent ACB-RFMs. In contrast, *TPRAC* employs activity-independent Timing-Based RFMs (TB-RFMs) that are both secure against RH and eliminate timing leakage.

**C. Defenses with DRAM Chip and Interface Modifications:** Several prior works propose redesigning the DRAM interface or chip internals to support concurrent mitigations or refreshes during activations [62, 110]. Because they avoid introducing explicit mitigation delays, these designs are resistant to timing channels. However, they require substantial modifications to both DRAM chips and the interface protocol, making deployment difficult. In contrast, *TPRAC* requires no such modifications and achieves timing-channel prevention based on the PRAC specification.

**D. RFM-Based Host-Side Defenses:** Host-side RH defenses mitigate attacks by issuing Directed RFM (DRFM) commands [41] to refresh neighboring rows, either probabilistically [44, 46, 49, 94, 113] or using trackers [6, 54, 73, 74, 79, 88, 91]. Tracking-based defenses monitor potential aggressors and issue DRFMs when activity crosses a threshold; this activity-dependent strategy introduces timing leakage. Probabilistic approaches issue DRFMs with a fixed probability on each activation, reducing susceptibility to timing channels, but failing to protect against RH at low N<sub>RH</sub> [35].

**E.** Alternative Mitigative Actions: Row migration [29, 86, 87, 89, 101, 104] and access throttling techniques [9, 105] mitigate RH by relocating or slowing access to frequently activated rows. However, these methods introduce noticeable latency variations, making them susceptible to timing channels. ECC-based defenses [2, 20, 65, 67–70] provide partial defense for RH but do not address timing leakage. In contrast, *TPRAC* is built on PRAC, preserving its RowHammer protection while eliminating timing channels.

## 9 Conclusions

This paper uncovers a critical security vulnerability in PRAC-based RowHammer mitigations, stemming from timing channels introduced by the Alert Back-Off mechanism and Refresh Management (RFM) commands. We present an attack called *PRACLeak*, which exploits these timing channels to create covert and side channels. This enables an adversary sharing a DRAM row with a victim to leak sensitive information – such as secret keys from vulnerable AES implementations – by monitoring memory access latencies.

To address this issue, we propose Timing-Safe PRAC (*TPRAC*), an activity-independent RFM mechanism that eliminates timing channels without compromising RowHammer mitigation. *TPRAC* introduces Timing-Based RFMs that are issued periodically and independently of access patterns to eliminate timing leakage. Our evaluation shows that *TPRAC* achieves robust security using only a single-entry per-bank mitigation queue and incurs just 3.4% performance overhead at a RowHammer threshold of 1024.

## Acknowledgments

We thank Stefan Saroiu for sharing insights on PRAC in his keynote at DRAMSec'24 that inspired this work. We also thank Aamer Jaleel for early discussions and feedback, as well as the anonymous reviewers of ISCA 2025 for their valuable comments. We thank UBC's Advanced Research Computing (ARC) team for their support [1]. This work is supported by the Natural Sciences and Engineering Research Council of Canada (NSERC) under funding numbers RGPIN-2019-05059 and RGPIN-2023-04796, and an NSERC-CSE Research Communities Grant under funding reference number ALLRP-588144-23. The views expressed are those of the authors and do not necessarily reflect those of NSERC, the Communications Security Establishment Canada, or the Government of Canada.

# Appendix A Artifact Appendix

## A.1 Abstract

This artifact supports two key aspects of the paper: (1) the proposed *PRACLeak* covert and side channel attacks, which exploit timing variations introduced by PRAC's mitigation actions, and (2) our defense, *TPRAC*, which uses activity-independent Timing-Based RFMs (TB-RFMs) to eliminate PRAC-induced timing channels.

For the *PRACLeak* evaluations, we provide the Ramulator2 [60] source code with modifications to support clflush along with required traces for experiments. We also include Bash and Python scripts to generate victim traces for AES T-Table encryption using the Ramulator trace generator, as well as the corresponding sender and receiver traces. Additional scripts are provided to run these traces in Ramulator2 and to reproduce the results shown in Figure 3 through Figure 5 and Figure 9.