# HARDWARE-ENABLED MECHANISMS FOR VERIFYING RESPONSIBLE AI DEVELOPMENT

# Aidan O'Gara<sup>\*1</sup>, Gabriel Kulp<sup>\* †2</sup>, Will Hodgkins<sup>\*3</sup>, James Petrie<sup>4</sup>, Vincent Immler<sup>5</sup>, Aydin Aysu<sup>6</sup>, Kanad Basu<sup>7</sup>, Shivam Bhasin<sup>8</sup>, Stjepan Picek<sup>9</sup>, and Ankur Srivastava<sup>10</sup>

<sup>1</sup>Oxford University, <sup>2</sup>RAND Corporation, Oregon State University, <sup>3</sup>Center for AI Safety, <sup>4</sup>Future of Life Institute, <sup>5</sup>Oregon State University, <sup>6</sup>North Carolina State University, <sup>7</sup>University of Texas at Dallas, <sup>8</sup>Nanyang Technological University, <sup>9</sup>Radboud University, <sup>10</sup>University of Maryland,

#### Abstract

Advancements in AI capabilities, driven in large part by scaling up computing resources used for AI training, have created opportunities to address major global challenges but also pose risks of misuse. Hardware-enabled mechanisms (HEMs) can support responsible AI development by enabling verifiable reporting of key properties of AI training activities such as quantity of compute used, training cluster configuration or location, as well as policy enforcement. Such tools can promote transparency and improve security, while addressing privacy and intellectual property concerns. Based on insights from an interdisciplinary workshop, we identify open questions regarding potential implementation approaches, emphasizing the need for further research to ensure robust, scalable solutions.

#### **Executive summary**

Recent years have seen dramatic progress in AI systems' capabilities, in large part achieved through scaling the amount of computation used in the training process. Displaying highly general capabilities, the most sophisticated AI models have the potential to generate significant economic value and help to solve pressing problems facing humanity, but could also facilitate various forms of malicious or harmful use. The potential role of AI hardware in promoting responsible AI development has recently attracted increasing interest from policy-makers and researchers (Kulp et al., 2024, The Bipartisan Senate AI Working Group, 2024).

This report outlines various hardware-enabled mechanisms that aim to advance certain AI policy goals based on functionality embedded securely into the hardware used to develop and run AI systems. We focus particularly on two classes of mechanisms: mechanisms that can enhance the visibility of governments, external auditors or other relevant stakeholders regarding how AI models are being developed, and mechanisms that can enable enforcement of regulations or agreements relating to high-risk AI development activities. For each mechanism, we discuss the current state of understanding regarding its technical feasibility, potential adversarial attacks, and open research questions. The mechanisms discussed here are not intended to provide an exhaustive list - for more extensive discussion of other options, see Reuel et al. (2024), Scher and Thiergart (2024) and Petrie et al. (2024). This report is based on a workshop held in August 2024 with researchers from hardware security, machine learning, and policy backgrounds to explore these questions.

**Verifiable AI training and inference.** Hardware-enabled mechanisms could support privacy-preserving and verifiable reports of certain AI workload properties such as quantity of compute used, data used, training techniques or instances of deployments that have occurred. They could also enable policy-makers or external auditors to perform sophisticated evaluations of AI models without direct access to the model weights. These mechanisms could strengthen external oversight and accountability, while respecting the legitimate IP and security concerns of model developers.

<sup>\*</sup>Equal contribution

<sup>&</sup>lt;sup>†</sup>Gabriel Kulp is currently serving as a Technology and Security Policy Fellow at RAND; however, the views, opinions, findings, conclusions, and recommendations contained herein are the author's alone and not those of RAND or its research sponsors, clients, or grantors.

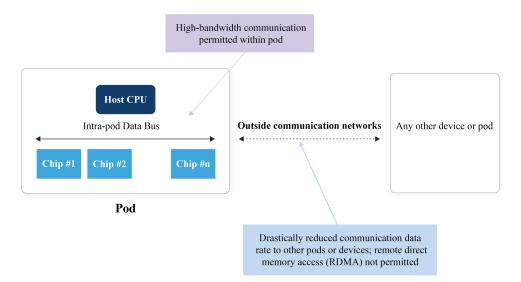

**Verifiable cluster configuration.** High-bandwidth communication between AI accelerators is a key requirement for training state-of-the-art AI systems, making it an important node for verification and enforcement of compliance with safety standards. Understanding which AI accelerators and other network components are connected to perform an AI training run can be valuable in verifying claims made about training computation, techniques or other properties. One potential approach to achieve these goals would be encrypted interconnection between components. This could help to verify cluster configuration and, if warranted by the risks and authorized by relevant regulations, enforce policies by limiting the number of AI accelerators that can be interconnected. In addition to this, such functionality could also enhance the security of AI systems during training and protect against unauthorized access to model weights or training data.

**Location verification.** In recent years, the US government and allied countries have introduced export controls on AI accelerators to limit their use for military and surveillance purposes by adversaries. Hardware-enabled mechanisms that accurately report a device's location could support well-targeted export controls and reduce the compliance burden by enabling chip owners to provide evidence that their chips have not been diverted to restricted entities. Such mechanisms could facilitate international cooperation to prevent proliferation of advanced AI hardware to untrusted actors such as terrorist groups or rogue states.

**Offline licensing.** In the future, under scenarios where risks from AI development warrant it or when dealing with less trusted actors, governments and AI developers may choose to enact licensing regimes for AI chips. High-performance AI chips could be designed with cryptographic mechanisms that only allow them to perform operations if they have a license to do so. This kind of licensing system could provide policy-makers and AI developers with more robust tools to enforce safety standards and regulations. In turn, such enforcement capacity would build confidence in mutual compliance, which would enhance incentives for developers and countries to cooperate internationally on AI safety standards.

**Open challenges.** Effective implementation of hardware-enabled governance mechanisms requires further investigation in several areas. Robust anti-tamper techniques will be essential to secure hardware against both non-intrusive and physical attacks by well-resourced actors, potentially up to and including state-level actors. Mechanism design must also ensure sufficient privacy protections for chip owners, preventing leakage of sensitive IP or unauthorized access to data. Given the heterogeneity of chip designs and of network topologies used by AI developers, mechanisms should also be flexible and adaptable to a variety of cluster configurations. The cost, operational impact and lead time to large-scale development are also important considerations for all these mechanisms.

# **Table of Contents**

| 1 | Intr | oductio | n                             | 4  |

|---|------|---------|-------------------------------|----|

|   | 1.1  | Motiva  | ation                         | 4  |

|   | 1.2  | Object  | tives                         | 7  |

| 2 | Mec  | hanism  | IS                            | 7  |

|   | 2.1  | Overv   | iew and scope                 | 7  |

|   | 2.2  | Verifia | ble AI training and inference | 8  |

|   |      | 2.2.1   | Related work                  | 8  |

|   |      | 2.2.2   | Technical details             | 8  |

|   |      | 2.2.3   | Attacks                       | 9  |

|   |      | 2.2.4   | Open research questions       | 9  |

|   | 2.3  | Verifia | ble cluster configuration     | 10 |

|   |      | 2.3.1   | Related work                  | 11 |

|   |      | 2.3.2   | Technical details             | 11 |

|   |      | 2.3.3   | Attacks                       | 12 |

|   |      | 2.3.4   | Open research questions       | 13 |

|   | 2.4  | Locati  | on verification               | 13 |

|   |     | 2.4.1   | Related work                                 | 14 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.4.2   | Technical details                            | 14 |

|   |     | 2.4.3   | Attacks                                      | 15 |

|   |     | 2.4.4   | Open research questions                      | 15 |

|   | 2.5 | Offline | Licensing                                    | 16 |

|   |     | 2.5.1   | Related work                                 | 16 |

|   |     | 2.5.2   | Technical details                            | 16 |

|   |     | 2.5.3   | Attacks                                      | 17 |

|   |     | 2.5.4   | Open research questions                      | 17 |

| 3 | Cha | llenges |                                              | 18 |

|   | 3.1 | Overvi  | ew                                           | 18 |

|   |     | 3.1.1   | Physical tampering                           | 18 |

|   |     | 3.1.2   | Privacy                                      | 19 |

|   |     | 3.1.3   | Time, operational and cost constraints       | 19 |

|   |     | 3.1.4   | Adaptability to future technological changes | 19 |

|   | 3.2 | Physic  | al Tampering                                 | 20 |

|   |     | 3.2.1   | Motivation and definitions                   | 20 |

|   |     | 3.2.2   | Research areas                               | 20 |

|   | 3.3 | Privac  | y                                            | 22 |

|   |     | 3.3.1   | Challenges                                   | 22 |

|   |     | 3.3.2   | Mitigations                                  | 23 |

| 4 | Con | iponent | S                                            | 25 |

|   | 4.1 | TCMs    |                                              | 25 |

|   | 4.2 | TEEs .  |                                              | 26 |

|   | 4.3 | Monot   | onic counters                                | 27 |

|   | 4.4 | Secure  | meters                                       | 27 |

|   | 4.5 | Secure  | memory                                       | 28 |

|   | 4.6 | RTCs    |                                              | 28 |

|   | 4.7 | Tampe   | r proofing                                   | 28 |

|   | 4.8 | Offline | power source                                 | 29 |

| 5 | Con | clusion |                                              | 30 |

# **1** Introduction

## 1.1 Motivation

AI has the potential to accelerate economic growth and support scientific breakthroughs. However, the current generation of AI systems have highly general capabilities, making AI a dual-use technology. Like any powerful technology, AI carries risks, including the possibilities of misuse by rogue actors and weaponization by nation states, as well as the potential for loss of control over AI systems. These challenges underscore the urgent need for robust safeguards and oversight mechanisms around AI.

**Misuse of AI capabilities could threaten public safety by lowering the barriers to launching powerful cyberattacks, developing biological weapons, and more**. Researchers have begun to characterize the nascent offensive cyber capabilities of LLMs (Zhang et al., 2024, Shao et al., 2024). In October 2024, OpenAI found that their newest o1 model "can help experts with the operational planning of reproducing a known biological threat, which meets our medium risk threshold" (OpenAI, 2024). As these dangerous capabilities continue to advance, minimizing risks of misuse by malicious actors is becoming a priority for AI developers and governments.

**Nation states could also weaponize AI for military purposes in ways that inadvertently increase the risk of armed conflict.** In 2017, Russian President Vladimir Putin said that whichever nation leads in AI "will be the ruler of the world." China's 2017 AI Development Plan set the ambitious goal for China to lead the world in artificial intelligence by 2030. The United States is actively pursuing the integration of AI into military systems, investing heavily in AI-enabled autonomous drones (In Focus, 2024). States might eventually become more involved in directly developing AI systems. Just as states have sought to limit the development and use of biological, chemical, and nuclear weapons, they might be interested in avoiding the worst-case outcomes of AI weaponization. Developing hardware-enabled mechanisms to help verify compliance with international agreements could enable cooperation on defining and enforcing acceptable use of military AI systems.

Misuse, weaponization and the disruption of strategic stability are the clearest and most immediate risks to national and international security, but other challenges loom on the horizon. There is the potential threat of loss of control over AI systems, either by voluntarily delegating decision making authority to AI systems to remain economically and militarily competitive (Hendrycks, 2023), or by accidentally developing rogue agents that deliberately seek power in ways unintended by their developers (Carlsmith, 2022). AI could also concentrate power in the hands of a small number of people, such as strengthening autocratic regimes by enabling widespread surveillance (Kalluri et al., 2023), or causing mass automation that leaves individuals dependent on corporations and governments (Acemoglu and Restrepo, 2019, Korinek and Suh, 2024). These challenges highlight the need for an approach to AI development that is not solely driven by commercial or competitive pressures, that provides for appropriate external oversight and scrutiny, and that promotes international cooperation on safety standards.

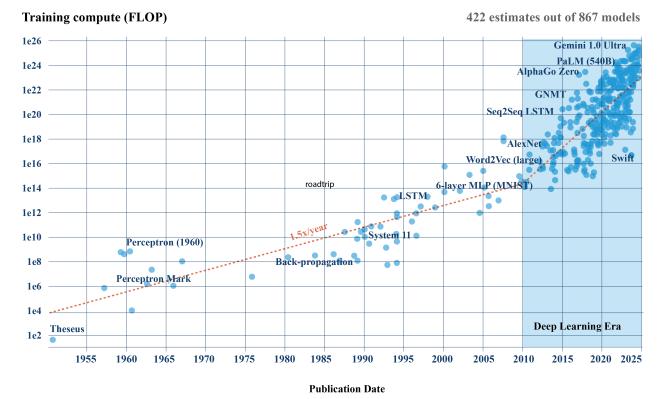

**Recent advances in AI have been driven to a large extent by growing hardware inputs.** The last decade of AI development has been governed by a simple paradigm: more computing power and more data allow neural networks to acquire more capabilities. Kaplan et al. (2020) formalized this insight, observing a mathematical power law relationship between the inputs to a neural network training run (compute, data, and parameters) and the network's performance, termed a "scaling law." To reap the benefits of these scaling laws, the amount of computational power used in the largest AI training runs has increased more than  $4 \times$  annually over the last decade (Epoch AI, 2024b). As an example, GPT-4 was trained with roughly  $1000,000 \times$  more compute than the original GPT model released in 2018, and each generation of GPT models has used roughly  $100 \times$  more compute than the last (Epoch AI, 2024b). The largest data centers currently under construction will cost billions of dollars and house hundreds of thousands of state-of-the-art GPUs (Nvidia and Broadcom, 2024, Epoch, forthcoming). The centrality of computing hardware in AI development makes it a promising node for governance.

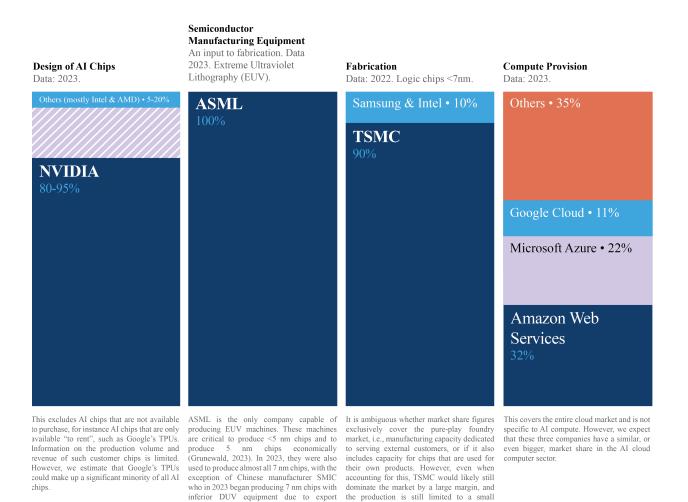

**Hardware is a promising lever for AI governance.** AI hardware appears to be a promising node for verifying compliance with responsible AI development practices. While other key inputs to AI development such as data and algorithms are non-physical resources that can be easily duplicated and shared around the world, hardware is a physical and excludable resource. The hardware supply chain is highly concentrated in a few companies—TSMC for chip fabrication, Nvidia for chip design, ASML and others for semiconductor manufacturing equipment—and these companies are predominantly located in countries allied with the United States. As of 2023, high-end data center AI chips represented less than 0.00025% of all chips produced (Heim and Pilz, 2024). Therefore, regulations that target these chips can likely be tailored to have minimal impacts on activities beyond AI development.

**Hardware-enabled mechanisms should target frontier AI development**. Available evidence from evaluations of current models suggests that they have limited capability to enable malicious actors to cause large-scale harm via cyber-attacks, bioweapons development etc., but that their capabilities in these domains are growing over time.

# Hardware-Enabled Mechanisms for Verifying Responsible AI Development

Figure 1: Notable AI Models. Adapted from: (Epoch AI, 2024a).

Therefore, frontier AI systems that raise the ceiling of capabilities in such domains are of greatest concern from a public safety and national security perspective. By frontier AI, we refer to general-purpose AI systems at or near the frontier of capabilities, such as Google DeepMind's Gemini 1.5 Pro, Anthropic's Claude 3.5 Sonnet, and OpenAI's o1. Only a handful of actors operate at the frontier of AI development, and each of them spends hundreds of millions of dollars or more in their efforts. They typically use a large number of advanced chips to train such systems (e.g. > 100,000 Nvidia H100s). It is both more feasible and more desirable to focus governance efforts on these large-scale AI developers relative to the large number of smaller actors that also use AI hardware, such as startups and academic researchers.

**Hardware-enabled mechanisms could further current and future goals in AI policy.** AI chips could be designed with technical mechanisms that enable AI governance. For example, the United States enforces export controls on high performance AI chips, but there is evidence of large-scale diversion of AI chips to controlled countries (Fist and Grunewald, 2023). Location verification mechanisms on AI chips could allow chip owners to demonstrate in a low-cost manner that they are still in possession of chips and are compliant with export controls. Another policy goal that could be supported by hardware-enabled mechanisms would be reporting of AI development activities to governments or other external bodies. For example, US Executive Order 14110 required developers to report to the federal government any AI system trained using more than 10<sup>26</sup> operations. Section 3 explains several such technical mechanisms and their purposes.

Hardware-enabled mechanisms can create optionality for policy-makers in addressing future governance challenges. Technical researchers today cannot anticipate all of the potential policy applications of hardware-enabled mechanisms, nor determine whether these policy applications will be desirable in the future. The risks presented by AI systems are evolving over time as capabilities continue to improve. However, given the significant lead time for making potential adjustments to the hardware or software used in AI development and getting these into commercial production, technical research on hardware-enabled mechanisms cannot be purely reactive. We believe the most productive role for technical research today is in creating a set of tools that AI developers and governments can choose to use (or not use) in the future. This increases the value of mechanisms that provide flexibility and can be tailored appropriately based on the risk landscape in coming years.

Figure 2: Concentration of the AI Chip Supply Chain. Expressed as percentage of total market share. Adapted from: (Sastry et al., 2024).

number of actors

inferior DUV

2023)

restrictions on EUV (Schleich and Reinsch,

Hardware-enabled mechanisms could reduce the need for expansive export controls. Firstly, if regulators are sufficiently confident that they can monitor what AI chips are being used for, there may be less of a need to prevent them from ending up in countries perceived as adversaries. This could be an incentive for companies to adopt the measures, as they might then be able to have a larger pool of customers to sell chips to. In practice, the confidence level might need to be extremely high to roll back export controls, and governments are likely to still want multiple layers of defense. However, it is feasible that hardware governance could at least reduce the likelihood of export controls being extended further to additional countries, and enable users in countries that are neither adversaries nor close allies to continue to use AI chips. For instance, if the US government were concerned about chips being smuggled to China through third countries, it might seek to extend controls to those third countries. Reliable location attestation could offer a way of knowing where those chips have ended up and deactivating them in export-controlled countries, allowing companies to continue selling chips to third countries.

Hardware-enabled mechanisms could allow companies to enforce their own terms of service. It might be useful for chip design companies, as well as regulators, to better understand what their hardware is being used for. Nvidia, for instance, makes different types of chips, some of which are intended for large-scale AI training in data centers, and other consumer-type GPUs designed for gaming. There have been examples of customers buying large numbers of the latter type and connecting them to do AI training, in breach of Nvidia's terms of service. This approach may be cheaper than purchasing GPUs intended for data centers, or enable companies to avoid using products subject to export controls. Companies may therefore stand to gain from monitoring activities, if it enables them to segment the market and restrict products to their intended uses.

## 1.2 Objectives

This report assumes that for large-scale AI computing to be safely integrated into society, several key sub-goals must be met. First, it must be governable, meaning that it should be possible to control access to large-scale AI computing, based on adherence to a shared set of commonsense rules, agreed by democratic nations, to prevent misuse that would create unacceptable risks to public safety and national security.

This level of oversight is desirable because government bodies are more likely to be able to pursue safety without being influenced by commercial incentives. Since the majority of AI development is currently happening in private companies, it is primarily driven by commercial incentives. Given strong competitive pressures to release products quickly in order to keep up with rivals, such incentives may lead companies to release AI models without adequately assessing and mitigating risks. Government bodies may be better positioned to push for strong safety standards, as well as to mediate cooperation between various stakeholders. International coordination is important to ensure rules are consistent across nations, thus avoiding regulatory arbitrage by companies.

A second sub-goal is that the use of large-scale computing must be verifiable; it should be possible to make reliable, externally verifiable claims regarding how computing resources are allocated and used, such as for specific training runs.

This verifiability is essential for the effective implementation of any regulations; it will be difficult to ensure that operators are adhering to rules without techniques and measures that can be trusted to report accurate information about how computing infrastructure is being used. Moreover, verifiable reassurance that actors are abiding by the regulations will be key to preventing security dilemmas. The latter can arise when organizations suspect that their competitors are breaching rules, creating a concern that they may fall behind if they stick to them. This can lead to a scenario in which all parties race ahead, lest rivals gain an advantage, collectively creating a riskier environment for everyone. Verifiable assurances that other parties are adhering to rules can foster a sense of trust and counteract pressures to race.

The third sub-goal for ensuring the safe deployment of large-scale AI is that computing infrastructure must be secure enough to withstand sophisticated attacks, safeguarding critical assets from malicious actors.

The potential power of large-scale AI models might create a strong incentive for some actors to evade hardware-enabled mechanisms and use them for disallowed activities. Mechanisms must therefore be robustly secured against skilled, well-resourced attackers. This will become increasingly important as AI is more widely deployed by a variety of companies and public services. If AI is integrated within critical infrastructure or running essential services, then successful attacks could cause significant harm and disruption.

Lastly, privacy-preserving measures are essential to uphold established data and code privacy norms and minimize the risk of harmful forms of surveillance. If not implemented carefully, hardware-enabled mechanisms could offer governments a way to increase surveillance, infringing on citizens' privacy and potentially suppressing legitimate activities. Companies may also be concerned about maintaining confidentiality of trade secrets. Guardrails that govern how third parties may access information and act upon it will be necessary to address these concerns.

# 2 Mechanisms

#### 2.1 Overview and scope

Previous work has underscored the potential for AI hardware to play a critical role in governance by enhancing regulatory visibility, enforcing safety standards, and mitigating risks from irresponsible or malicious AI development (Sastry et al., 2024). This section explores hardware-enabled mechanisms that can support compliance with regulation, safety standards and corporate policies, strengthen external oversight, and protect intellectual property against potential threats. These mechanisms are particularly relevant for promoting responsible AI development and fostering international cooperation on safety standards.

Hardware-enabled mechanisms refer to solutions that aim to advance certain AI policy goals (e.g. transparency or non-proliferation of hazardous AI systems) based on functionality embedded into the hardware used to develop and run AI systems. In this context, hardware is not restricted to AI accelerators and may include other relevant components such as network interface cards or network switches. Solutions that are embedded in relevant hardware do not necessarily require modifications to existing hardware designs. They may instead be achievable purely through software updates such as changes to firmware or drivers, taking advantage of existing features such as Secure Boot or Trusted Execution Environments (TEEs).

We provide an overview of four key mechanisms for AI governance:

- 1. Verifiable AI training and inference. Privacy-preserving, hardware-enabled mechanisms could enable the generation of trustworthy, verifiable measurements of AI workload properties, such as workload size or operational hours. In addition, these mechanisms could allow policy-makers or auditors to conduct a wide range of evaluations without direct access to model weights, bolstering accountability while safeguarding IP and security concerns.

- 2. Verifiable cluster configuration. Understanding the number of AI accelerators connected in high-bandwidth configurations can help to verify claims made about the number of operations or other properties of AI training runs. If warranted by the risks and authorized by relevant regulation, limits on the size of a training cluster could be used to limit high-risk AI training activities while maintaining functionality for smaller-scale training and inference.

- 3. Location verification. Secure hardware-based location reporting could support export controls and prevent AI chips from being diverted to untrusted entities. Over time, such mechanisms could underpin international agreements restricting access to advanced AI hardware to actors that adhere to responsible AI development standards. This could simply provide visibility to regulators, or could be combined with other mechanisms to enable geographically targeted policy enforcement, such as geolocking of AI accelerators in prohibited locations.

- 4. **Offline licensing.** If warranted by the risk level posed by AI training or inference activities, or when dealing with untrusted actors, chips could be designed to require a license for use. These licenses would be cryptographic keys issued by a regulatory authority that expire after a specified amount of computational work, requiring the chip owner to acquire a new license. These licenses could ensure compliance with safety standards and enable more robust governance in certain scenarios.

While this is not an exhaustive list, these mechanisms represent promising tools to enhance the governance of advanced AI systems and create incentives for international collaboration on AI safety.

#### 2.2 Verifiable AI training and inference

AI chips could be designed to generate verifiable digital certificates that attest to key aspects of device operation, such as the size of an AI workload or the number of hours the device has been active. These certificates would support regulators in identifying and monitoring high-risk AI training activities. Certification could be particularly valuable for verifying compliance in lower-trust environments, such as when commercial or geopolitical competitors agree to comply with certain AI standards. Properties that might be verified can be split into at least three sets with distinct technical requirements:

- **Compute accounting** could be facilitated by providing signed measurements of the computational activity carried out as part of an AI training run. Such measurements would be valuable for regulatory compliance with policies that require reporting if a model's training goes above a certain computational threshold (e.g., US Executive Order 14110, EU AI Act). They could also be useful for environmental impact tracking.

- Workload classification aims to distinguish AI from non-AI workloads, or AI workloads at different stages of the model lifecycle (design, pre-training, post-training enhancements, and deployment), to ensure that monitoring activities are appropriately targeted.

- **Detailed workload verification** involves verifying properties of the AI model or training dataset, for example verifying whether the dataset contains high-risk content (e.g. data relevant to building weapons) or confirming that certain safety evaluations have been conducted.

#### 2.2.1 Related work

Heim et al. (2024) provide an extensive discussion of methods for workload classification and measurement in AI systems. Some approaches to measuring AI training activities include the use of remote attestation within a secure hardware module, such as a trusted execution environment (TEE), as suggested by Aarne et al. (2024), or the concept of "training transcripts," which involve saving snapshots of model weights during training, as proposed by Shavit (2023).

#### 2.2.2 Technical details

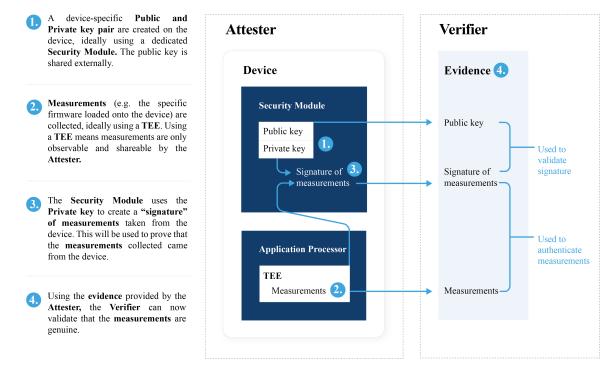

**Compute Accounting.** To implement compute accounting, the chip would require meters to monitor relevant metrics, such as clock cycles or other indicators of computational activity. These measurements would ideally be collected using a trusted execution environment (TEE) or other secure enclave. The chip would generate a device-specific public and private key pair, ideally through a dedicated security module. The public key would be shared externally

Figure 3: Adapted from: (Heim et al., 2024).

before measurements are taken, while the private key would be used to create cryptographic signatures of the device's measurements. This allows a verifier to validate the authenticity of the measurements, confirming that they genuinely originated from the device.

**Workload Classification.** For workload classification, robust indicators must be identified to distinguish AI-related workloads from other operations. Indicators like the scale and configuration of hardware provide valuable clues to this. For more granular classification, heuristics based on technical characteristics could be manually defined, or machine learning classifiers can be trained using cluster- and node-level data. Frontier-scale AI training, for example, could be identified by unique patterns, such as the number of accelerators, steady peak throughput utilization, and specific communication patterns within nodes that correspond to different forms of parallelization.

Classification could be performed using measurements from individual AI chips or other devices such as network switches. Hardware-backed classification approaches could provide greater confidence that reports genuinely originated from the AI hardware that is intended to be monitored.

**Detailed Workload Verification.** Detailed workload verification seeks to provide assurances about governance-relevant properties of a workload without requiring direct access to customer code or data, preserving confidentiality. Techniques like confidential computing can allow customers to prove specific aspects of their workloads to compute providers or regulators. For instance, customers could demonstrate that they used or avoided particular datasets or performed specific model evaluations. Secure enclaves such as TEEs could help with running these verifications without exposing models or sensitive data.

#### 2.2.3 Attacks

Potential attacks on these monitoring approaches include tampering with secure enclaves, meters, or other components to corrupt or falsify measurements. Adversaries might target the security mechanisms of trusted execution environments (TEEs) or meters to forge or manipulate data.

Adversaries could intentionally modify the computational patterns of their workloads to avoid triggering classification as AI-related tasks. For example, they might introduce noise by adding irrelevant computational activities that make classification more challenging.

They might also fragment their activities, distributing workloads across multiple data centers or compute providers, making it difficult for verifiers to get a clear picture of the total computational effort involved.

#### 2.2.4 Open research questions

• What are the most effective metrics and indicators for accurately classifying AI workloads and performing compute accounting, while minimizing performance overhead?

Figure 4: Adapted from: Aarne et al. (2024).

- How can adversarial robustness be improved for these metrics, ensuring resilience against intentional manipulation and evolving AI training techniques?

- What are the technical and practical challenges of implementing large-scale cryptographic proofs and secure enclaves (e.g., TEEs) for AI verification across multi-node and multi-GPU systems? What modifications to current hardware, protocols, and security features would be needed to enable widespread use of TEEs for verifying governance-relevant properties of AI training at scale?

- How can dataset verification be reliably performed in distributed systems, accounting for challenges like pipeline parallelism and data parallelism, where only subsets of GPUs interact with input data?

#### 2.3 Verifiable cluster configuration

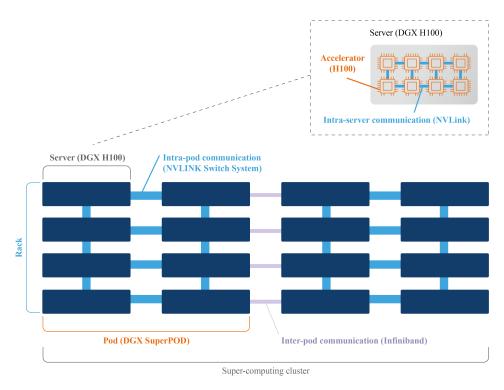

High-bandwidth interconnection is essential to enable training of frontier AI systems based on current training techniques. In order to ensure that reported measurements of AI training activities are complete, it is important to understand how an AI training cluster was configured and which devices were included. Failing this, adversaries may engage in selective reporting of their training activities and conceal certain aspects. Mechanisms that provide regulators or auditors with improved visibility into the number of AI accelerators used in a particular training run, or that allow AI developers to make verifiable claims about this, would be valuable to support external oversight of compliance with safety standards.

In certain scenarios where the risk of harm is sufficiently high, it may also be desirable to prevent unauthorized actors from aggregating high-performance AI chips into large-scale supercomputers for AI training. To achieve this, restrictions could be implemented on the ability of these chips to interconnect to form clusters. Two potential approaches could achieve this. The first involves configuring a fixed set of AI chips into a predefined pod that allows high-bandwidth interconnection within the pod, but severely limits external communication with devices outside the pod, making it difficult to combine multiple pods for large-scale AI training. The second approach would loosen the restriction of a predefined pod and instead rely on an adjustable cap on the total number of interconnected AI chips or total interconnect bandwidth between them. This cap could be adjusted depending on which activities a particular chip owner or operator is authorized to conduct.

Figure 5: AI Computing Cluster. Adapted from: Kulp et al. (2024).

## 2.3.1 Related work

Kulp et al. (2024) introduce the concept of a "fixed set" with a pre-configured set of AI chips and limited external communication bandwidth. Petrie et al. (2024) discuss the potential role of encrypted interconnect in implementing controls on the number of interconnected GPUs.

#### 2.3.2 Technical details

One approach to verify and enforce specific configurations of devices involved in an AI cluster is the **fixed set** approach. This involves assembling AI chips into an integrated pod, where each chip is pre-authorized to interconnect only with other chips within that pod. The integrity of the connections between the chips and resistance to tampering could be assured using a hardware Root of Trust. Chips should be able to perform tests to detect unauthorized changes and be disabled if relevant changes are detected, such as chip firmware modifications or connection of additional chips to a particular pod.

A potential alternative is the **adjustable cap** approach, where each AI chip is equipped with a secure cryptographic ID, allowing it to authenticate the identity of other interconnected chips. Using public key cryptography or similar mechanisms, chips validate these IDs before exchanging data, ensuring that communication is limited to authorized chips. A cap on the number of chips that each AI chip can communicate with is enforced, which can be adjusted only with authorization from a trusted entity, such as a regulator. Chips periodically check this cap, and if the cap is lowered, they automatically limit or shut down communication with other chips. Similarly to the fixed set approach, to ensure the integrity of the mechanism it would be important that chips are able to detect unauthorized changes and that they no longer function if such changes are detected.

For both approaches, there is a question of what physical or software components within an AI cluster should be used to monitor the cluster configuration and enforce compliance. For a friendly actor, the easiest solution may involve management software, which can already expose rich information on a cluster's configuration to operators. Examples of such software for Nvidia products include NCCL (NVIDIA, 2024) at the framework level, UFM (UFM, 2024) at the networking level, or DCGM (DCGM, 2024) at the cluster level. However, it is unclear whether such software can be mandated and used to securely enforce restrictions without opening up low-cost opportunities for tampering or circumvention. In addition, data centers used for AI clusters employ different network topologies (e.g. Patel et al., 2023) and equipment from different suppliers which may have different associated management tools (e.g. Nvidia and

Figure 6: Adapted from: (Kulp et al., 2024).

Broadcom, 2024). Given this heterogeneity, it is unclear how feasible it would be to adapt existing management systems to enforce restrictions across all possible combinations of hardware.

Alternatively, chip-to-chip interconnection could be limited at the level of individual equipment units and their firmware. This equipment could include either AI chips or networking equipment such as switches. This approach faces a different challenge: compute and networking components may face limitations on their ability to gather and interpret information about the cluster topology. For example, a host CPU in a server can see the local PCIe and network interfaces, but may lack information about the cluster's global topology. NICs and switches also only receive information about directly connected devices.

To address these issues, one potential solution could be encryption of all outbound interconnect traffic from highperformance AI chips. The provisioning of keys to decrypt this interconnect traffic could be used to limit the number of AI chips that can be interconnected. Encrypted interconnect could provide other benefits such as protecting weights from being exfiltrated by an attacker snooping on interconnect. It is also likely required for multi-GPU confidential computing, which can enhance the security of AI models against theft while they are in use on AI chips.

Nvidia's H100 chip already has dedicated AES-GCM hardware to encrypt PCIe traffic for single-GPU confidential computing. To enable multi-GPU confidential computing, AES-GCM hardware for the NVLink ports would likely also be required to ensure interconnect traffic is secure against interception. This suggests that future generations of AI chips may be equipped with the required encryption hardware to enable encrypted interconnect. However, if required hardware is not added, a potential alternative would be the use of occasional randomized authentication challenges, though this would likely provide lower levels of security.

More generally, a solution would need to be dynamic to account for swapping out units periodically, since the failure rate of AI chips (and networking equipment) in large clusters is non-negligible. This may be a particular challenge for the "fixed set" approach.

#### 2.3.3 Attacks

Potential attacks on the integrity of these mechanisms could involve various strategies to bypass the restrictions on inter-chip communication. This could involve directly tampering with the mechanisms or circumventing restrictions to enable sufficient inter-chip communication for large-scale training.

In the **fixed pod** approach, adversaries might attempt to compromise the pod's Root of Trust or otherwise tamper with the system to connect additional unauthorized chips, allowing for larger-scale AI training beyond the preauthorized set. For the **adjustable cap** system, attackers could target the mechanism that enforces the cap on the number of interconnected chips, for example through physical tampering or attempting to broadcast instructions to the chip to raise the cap to levels not intended by authorized parties.

More generally, it may be possible to split the workload between supposedly separate clusters using data parallelization. If a small number of devices can be compromised, these could act as a bridge to smuggle in the averaged gradients between the separate clusters. If tampering to compromise devices is feasible but costly, this could significantly reduce the overall cost of circumventing restrictions compared to other mechanisms that would require every single device to be compromised.

To circumvent restrictions, data could be transferred indirectly via the PCIe connection to the CPU, using it as a bridge to other AI chips, instead of via direct chip-to-chip connections such as NVLink. This would likely result in a performance penalty relative to standard training approaches. To further deter this, it may be possible to increase the latency of PCIe connections.

**Decentralized training could present a larger challenge in future.** As decentralized AI training techniques improve (Peng et al., 2024, Patel et al., 2024, Prime Intellect, 2024), attackers could exploit these advancements to use lower bandwidth between pods, making it feasible to coordinate large-scale AI training even when communication between pods is intentionally limited. Beyond the need to govern hardware at the level of a cluster, there may also be a need in future to govern systems of multiple clusters, which might even be situated in different countries. While the GPUs involved in training an AI model are usually located in a single data center or campus, there is strong interest from AI developers in performing training with a combination of several smaller clusters that are geographically separated.

This would increase the complexity and cost of implementing hardware-enabled governance mechanisms. For instance, if it is already a challenge to determine the boundaries of a single cluster, it may be yet more difficult to determine how many separate clusters are involved in a training run. Additionally, more distributed systems might vastly increase the number of entities that could contribute to training and whose hardware would be relevant to governance. Expanding the scope of monitoring and enforcement would exacerbate concerns about privacy and other impacts.

If decentralized training achieves sufficient performance to train AI systems with concerning capabilities, the greatest impact would likely be on mechanisms involved in workload attestation and cluster configuration limits, as it may be difficult to detect how large the effective cluster is and to establish broader, meaningful properties of its workload. Licensing and location attestation systems are less likely to be affected.

#### 2.3.4 Open research questions

- What is the optimal mechanism of implementation for monitoring and enforcing chip interconnection limits? For example, how feasible is the use of cluster management software, network switches or individual AI chips for this purpose?

- How viable are secure, remote, post-manufacturing adjustments to previously specified limits on communication bandwidth? Can flexible caps or whitelists for interconnection of AI chips be implemented without creating security vulnerabilities that would make the system easy to bypass for moderately resourced actors?

- What are the appropriate technical parameters for pod size and external communication bandwidth limits, given current AI training needs and anticipated future developments in distributed AI training techniques?

- How can heterogeneous devices be identified in a secure way? How can individual device authentication or attestation mechanisms be integrated into a cohesive architecture that verifies and controls the number of interconnected AI chips?

- How can the integrity of fixed set pods be remotely attested, and what mechanisms could be developed to detect tampering with these configurations?

- If restrictions are enforced using networking equipment, how can this be done without undesired impacts on non-AI training activities that use this equipment?

- Is there a way to securely update which chips are permitted in the pod so that broken hardware can be replaced?

## 2.4 Location verification

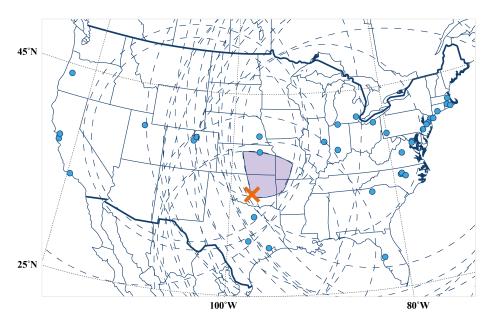

AI chips could be designed to make it possible for an external regulatory authority to securely and reliably determine their location and take policy actions based on a chip's location. Alternatively, the chip could determine its own location and respond directly, such as restricting operation when located in an area known to be subject to export controls. There are a number of technical approaches to location verification which can be used alone or in tandem to provide location estimates that are accurate and robust against adversarial tampering.

#### 2.4.1 Related work

Brass and Aarne (2024) provide an overview of the motivations and mechanisms for geolocation of AI chips for a general audience. There is an extensive research literature on the technical challenges of geolocation of devices in a non-AI context, which we discuss below.

#### 2.4.2 Technical details

AI chips could participate in **challenge-response protocols** with landmark servers in known locations. Chips would establish an encrypted connection with a server over the internet, then receive and respond to a challenge sent by the server. The server would authenticate that the chip's response is signed by a private key unique to that chip, and would measure the time taken by the chip to respond to the challenge. This time delay could be converted into an estimate of the chip's distance from the server, and the chip's location could be triangulated using estimates of its distance from several landmark servers.

One technical issue with challenge-response protocols is estimating the chip's distance from a landmark server based on the amount of time taken by the chip to respond to the server's challenge. The relationship between response delay times over the Internet and distance can vary depending on how direct the routing path is, network congestion, or other factors. Some previous efforts have employed fixed ratios for converting delay times to distances (Maram et al., 2021), while others have developed distance functions (Laki et al., 2011, Padamanabban and Lealkshminarayanan, 2001, Sheng et al., 2024, Kohls and Diaz, 2022, Gueye et al., 2004, Wong et al., 2007) to account for specific factors that drive variation in communication times.

Another technical challenge with challenge-response protocols is triangulating a chip's location based on estimates of distance to individual servers. A straightforward approach would be to trace circles around each landmark using the distance estimates, and intersect them to define a region in which the target is likely located (Gueye et al., 2004, Wong et al., 2007), but more complex approaches may improve accuracy. One alternative is to define location probability regions using historical data for each landmark, and return the location with the highest likelihood in the joint distribution of all landmarks (Laki et al., 2011, Padamanabban and Lealkshminarayanan, 2001, Arif et al., 2010). Abdou et al. (2015) select three landmarks defining the smallest possible triangle in which the target claims to be located and use trigonometric approaches to verify if the target is actually located inside the triangle. Sheng et al. (2024) use trigonometry to estimate the maximal possible distance between the claimed location and actual location of the target in every possible direction for each landmark. They then combine these observations to trace a region of possible geolocation. Importantly, their protocol is robust to a percentage of compromised landmarks, providing Byzantine fault-tolerance. Kohls and Diaz (2022) use gradient-descent based optimization techniques to find the most likely location based on a set of distance estimates from different landmarks.

Figure 7: By combining delay measurements from multiple landmarks, it is possible to estimate the location of an AI chip over the Internet or satellite networks. Adapted from: Gondree and Peterson (2013).

**Network infrastructure data** could provide additional validation of challenge-response geolocation results. Analysis of traceroute data and DNS records can help verify whether the network path taken by packets is consistent with measured distances. Further validation could come from consulting free or commercial Internet topology databases that contain IP address information. Internet Service Providers (ISPs) could also provide detailed network topology information, while chip users could report their ISP affiliations, offering additional cross-verification of the measured locations. These network-based validation methods, while not sufficient on their own, can serve as complementary verification mechanisms to strengthen the overall confidence in location estimates.

**Satellite systems** might be able to provide more secure and accurate geolocation by routing traffic from landmarks over satellite connections or even by locating landmarks on satellites. GPS systems are vulnerable to location spoofing attacks, but other services such as STL (Satellite Time and Location) and authenticated GNSS services like Galileo OS-NMA may provide greater protection against spoofing. This would likely require AI chips' owners or users to set up antennas to connect to satellites, and the operators of the geolocation scheme to pay for access to relevant satellite services. In addition, to defend against certain types of attacks such as replay attacks, there may be a need for a secure clock near the chip to act as a reliable source of time measurements. Assuming that satellite connections can provide sufficient security and that the cost to use satellite infrastructure is manageable, these could serve as a complement or a substitute for internet-based challenge-response protocols. This could be particularly valuable in situations where unusually high levels of accuracy are required, such as for AI chip users that are located close to borders with countries subject to export controls.

## 2.4.3 Attacks

We highlight three main classes of attacks against challenge-response geolocation: manipulating response times, interfering with landmarks, and tampering with chips.

Response times could be manipulated to be slower or faster than normal. Slower responses would raise uncertainty about a chip's location, but this might not be problematic, as regulators could simply identify this anomaly and assume the worst: if measurements cannot rule out that the chip is located in a restricted location, they could assume that it is. Faster response times would be more concerning, as this would make a chip appear closer to a landmark than it is in reality. These may be possible by using satellite connections or private terrestrial connections (for example by renting dark fiber) that can avoid potential delays due to circuitous routes or congestion affecting traffic sent over the Internet. To guard against this risk, many landmarks could take many measurements, making it difficult for an adversary to consistently spoof a single location. Alternatively, rather than manipulate the chip's response times, the calibration of the landmarks could be manipulated to cause the regulator to consistently misidentify chip locations. Collusion between an adversary and an internet service provider could make these attacks easier.

Landmark servers could be manipulated in several ways. They could be subject to distributed denial of service (DDoS) attacks, rendering them unable to participate in geolocation protocols. Cyberattacks against a landmark's clock or timestamp system could cause it to misreport the amount of time taken for chips to respond. Attackers could attempt to locate landmark servers to inform their efforts to spoof a chip's location by speeding up and slowing down responses. Defenses against all of these attacks would involve having many landmark servers with strong cyber- and physical security that conduct repeated efforts at geolocation.

Owners of chips could tamper with their devices to undermine the cryptographic protocol. In this system, chips would sign their responses with a private key. If the chip's owner can read that key and load the key onto another chip that can run the same protocol, then that chip could be placed in a different location and used to respond to challenges from landmark servers. This would effectively spoof the geolocation protocol. Success in challenge-response geolocation will require that chips contain private keys which cannot be read by chip owners.

### 2.4.4 Open research questions

- Given that the delay to distance relationship varies depending on local network conditions, what level of accuracy in location estimates is feasible in various regions of the world, particularly those in and around countries subject to export controls on AI chips?

- What improvements are possible on existing protocols for converting time delays to distances and distances from individual servers to absolute locations?

- How can location verification protocols be calibrated or complemented with other tools to minimize the rate of false positives, which could lead to unnecessary operational disruption for chip users?

- How scalable are the proposed location verification protocols, and what modifications might be required to enable location verification for millions of high-performance AI chips?

- Given their potential for greater accuracy, can satellite-based communications provide a sufficiently secure and economically feasible alternative to communication over the Internet for verifying locations?

- How can landmarks be secured against DDoS and other kinds of attacks?

- How can secure memory protect private keys from being read by chip owners?

- How can this protocol be made compatible with desires for strong cybersecurity at data centers that might involve airgapping?

#### 2.5 Offline Licensing

In certain scenarios, AI developers or governments may wish to implement licensing regimes for AI accelerators. For example, when exporting AI chips to countries with a heightened risk of theft of AI chips or onward re-export towards export-controlled countries, it may be desirable to introduce licenses that limit the benefits of such activities by restricting the chip's functionality if it is stolen or diverted. More generally, this licensing mechanism would prevent the unlicensed use of AI chips, providing a flexible mechanism to monitor and control AI development and deployment in cases where the risks warrant such a scheme and where it is authorized by national regulation or corporate policies. Licenses could be implemented in the form of cryptographic keys that act as temporary passwords, unlocking a chip's capacity to perform a specified amount of computational work, such as a set number of operations or memory transfers. Once this computational work has been performed, the license would expire, and the chip would shut down or operate only at a reduced capacity. The chip operator would then need to acquire a new license from a license provider to resume full use of the chip.

#### 2.5.1 Related work

Kulp et al. (2024) proposed licensing as a mechanism for AI governance, and Petrie (2024) detailed a specific implementation of a licensing mechanism. This licensing mechanism is closely related to Secure Boot (Secure Boot, 2024), a common security feature on personal computers that checks the cryptographic signature of a system's firmware to ensure authenticity before booting the system. One example of a licensing system that has already been deployed for commercial purposes is Intel On Demand (Intel, 2024), which requires customers to purchase licenses to unlock certain chip functionality. There is plenty of existing work on secure boot in general, but research on hardware-based AI licensing mechanisms is currently nascent.

#### 2.5.2 Technical details

Three core components of any licensing mechanism are licenses, meters, and throttling actions (Kulp et al., 2024).

*Meters* would track the computational capabilities that are intended to be licensed and limited. Many different metrics could be metered, including "wall-clock time, uptime, total energy intake (watt-hours), multiply-accumulate operations, amount of data transfer to memory (bytes) through the GPU's memory physical interface (PHY), or any other indicator of use that can serve as a workload distinguisher" (Kulp et al., 2024). Many of these metrics are already tracked on modern GPUs. Petrie (2024) argues that clock cycles are a good choice for a single metric to monitor, as they are relatively easy to track with lower risk of tampering and serve as an effective proxy for the number of operations used in training neural networks. Tracking multiple metrics might provide additional benefits, such as creating redundant measurements that reduce risks from tampering and providing flexibility to regulators in case the key inputs to AI development change over time.

| Resource                                    | Workload Target                                            |

|---------------------------------------------|------------------------------------------------------------|

| Floating-point arithmetic unit uses         | High-accuracy matrix multiplication                        |

| Integer arithmetic unit uses                | High-speed matrix multiplication                           |

| Memory transfer volume                      | Weights, activations, and dataset batches                  |

| Interconnect transfer volume (e.g., NVLink) | Distributed training, distributed inference                |

| PCle transfer volume                        | Model checkpointing, distributed training, dataset batches |

| Joules (watts $\times$ time)                | Hardware utilization                                       |

| Clock cycles                                | Hardware utilization                                       |

Table 1: Potential Targets of Metering. Adapted from: Kulp et al. (2024).

*Throttling actions* would limit or eliminate computational capabilities when a valid license is not present. These actions could throttle only one of the capabilities (e.g. memory transfers) while leaving others intact, or could limit

all capabilities at once. Capabilities could be eliminated entirely or merely restricted to a reduced level. Secure Boot already implements an extreme form of throttling action, as the chip doesn't boot if the firmware isn't authentic. Further work is required to understand methods for circumventing throttling actions that are possible with current chips and for resisting these attacks.

*Licenses* specify the amount of computational work that the owner of the license should be allowed to perform. This is a digital license which the chip itself reads and is unrelated to other forms of licensing such as export approval licenses for AI chips. A license provider could cryptographically sign their licenses with a private key and, if chips store the license provider's public key in unmodifiable memory, then chips would be able to distinguish authentic licenses from counterfeits. Licenses could also include other information, such as the ID of the license itself and an ID number for the device to which the license is intended to apply.

## 2.5.3 Attacks

We outline several categories of attacks on licenses and propose specific modifications to the licensing system design to thwart these attacks (Petrie, 2024):

- First, to prevent chip operators from creating their own counterfeit licenses, the license provider could sign each license with their private key, and chips could be built to store the license provider's public key in secure, tamper-resistant memory, allowing the chip to verify that the license's signature is authentic.

- Second, to prevent the same license from being used multiple times on a single chip, the license could include a license ID that starts at zero for the first license issued to a particular chip operator and increments up with each new license. The chip could be designed to reject any license ID lower than the chip's most recently used license ID number, thus preventing old licenses from being reused.

- Third, to prevent the same license from being used for multiple chips, chips could be built with an unmodifiable Device ID, and licenses could specify the Device ID of the chip they're intended to license.

| Data                               |  |  |  |

|------------------------------------|--|--|--|

| License ID: 3                      |  |  |  |

| Device ID: 00001347890             |  |  |  |

| Usage Allowance: 1000000000000000  |  |  |  |

| Signature of Data: 4F2E7ADFB21233D |  |  |  |

Figure 8: Example License. Adapted from: Petrie (2024).

The license itself is not the only component of the mechanism that could be attacked. Tampering with meters could cause inaccurate logging of chip usage, allowing the chip to be used beyond its licensed capacity. If the throttling mechanism can be circumvented, then the chip can similarly be used illicitly. Powering off a chip could enable mechanism tampering. More broadly, secure non-volatile memory is an essential component of the proposal in Petrie (2024), required to store the device ID and the license provider's public key.

#### 2.5.4 Open research questions

Topics requiring further research related to this proposal include:

- To what extent are existing secure boot technologies appropriate for protecting licensing (and other hardwareenabled governance mechanisms) against tampering? What new vulnerabilities could arise in this context and how can these be mitigated?

- How can the authenticity of licenses be verified in a scalable way across hundreds of thousands of chips? What other implementation challenges should be expected in deploying a licensing scheme at scale, and how can these be addressed?

- Which quantities should be metered, and how can this be done securely? What are the strengths and limitations of potential candidate metrics such as floating-point arithmetic unit uses?

- What technical and operational constraints should be considered when determining how much of each quantity should be allowed per license? Smaller limits would require chip owners to more frequently renew their licenses, which has costs and benefits from a governance perspective.

- How should licenses be issued? This is primarily a policy question, not a technical question. However, technical researchers could enable more desirable policy choices, such as designing systems for multi-party provision of licenses that enable multilateral AI governance.

## **3** Challenges

#### 3.1 Overview

Developing and implementing the mechanisms discussed in this paper will present some important challenges, ranging from security measures to protect the integrity of their functionality to meeting operational constraints to ensure they can be deployed at scale. We will now outline some of the main obstacles that will need to be overcome to realize these mechanisms in practice.

#### 3.1.1 Physical tampering

**Hardware-enabled mechanisms must be secure against potential adversaries.** Hardware-enabled mechanisms might provide the most value in adversarial environments where legal remedies or other existing approaches cannot be trusted. For example, if various national governments wish to make an agreement about frontier AI development, they will need trustworthy mechanisms for verifying compliance with the agreement that cannot be evaded by either side. Hardware-enabled mechanisms might play a special role here.

To characterize the different kinds of adversarial settings, each with different requirements for security against adversaries, we follow the taxonomy from Aarne et al. (2024):

- 1. "Minimally adversarial contexts, where attackers do not spend much on attacks, and are very averse to being discovered attempting to compromise mechanisms"

- 2. "Covertly adversarial contexts, where attackers are more willing to spend substantial resources to compromise mechanisms, but still want to avoid being caught doing so"

- 3. "Openly adversarial contexts, where attackers are willing to spend very significant resources to compromise mechanisms and are indifferent to this being discovered."

Physical security against tampering will need to be prioritized. Historically, one of the major motivations for work on chip security has been to preserve users' privacy and confidentiality, by guarding against attacks that aim to infer secret information, hijack control flow, compromise system root-of-trust or steal intellectual property (Hu et al., 2020). However, monitoring the activities of AI chips to ensure they do not violate regulations or agreements implies a different kind of threat model, in which the users themselves could be attackers. Under this new paradigm, anti-tampering measures will be essential to prevent people with physical access to GPUs from physically altering the mechanisms to circumvent restrictions.

**Anti-tampering measures may need an unusually high level of reliability in the context of hardware-enabled mechanisms.** Covertly evading compliance with the policies enforced by hardware-enabled mechanisms could potentially confer significant economic or military advantages. As a result, AI developers, governments or other actors may be strongly motivated to attempt to tamper with relevant AI hardware to disable or compromise these mechanisms. For regulators to trust the mechanisms, and for companies to adopt them, there will likely need to be strong evidence that they are robust and that it is sufficiently costly to circumvent them.

A defense in depth approach could improve stakeholders' confidence in the mechanisms' security; by layering multiple defense features, designers can reduce the likelihood of an adversary managing to bypass all of them and conduct a successful attack. These defenses could include destructive responses, such as hardware deactivation or data deletion.

System designs that reduce the attack surface could also be explored as a potential way of improving security and confidence. This might be done by running monitoring and enforcement operations on well-encrypted, trusted components like hardware security modules, for example, minimizing the number of components that need to be defended.

Formal verification of how software components function under different attack conditions could also provide strong evidence of their security. Although it would likely be unfeasible to obtain exhaustive proof for every single component under every relevant set of circumstances, it may nevertheless be valuable to pursue the most security-critical ones.

Finally, routine auditing for compliance with FIPS-inspired standards tailored to AI hardware could offer governments and operators additional reassurance of the mechanisms' security.

All these ideas require extensive research into the details of their implementation and the level of confidence they can provide, but they may be useful starting points for the development of the highly robust security needed. We will explore some of the technical requirements and concepts for possible anti-tamper measures in more detail later in this section.

## 3.1.2 Privacy

**Communication of data off-chip will need to be highly secure and limited in scope.** AI chips will need to share data beyond the chip for some of the mechanisms described above. Companies and chip users may be concerned that this could create new vulnerabilities, increasing the risk that their intellectual property or other sensitive data might be leaked or stolen. Measures will need to be taken to provide assurances to chip users regarding controls of which data can be shared beyond the chip, as well as to ensure strong information security practices on the part of those receiving any data.

If regulators have too much access to information about chip activities and too much power to restrict their usage, this centralization of control could bring its own risks (Sastry et al., 2024). There may be concerns about misuse or overreach in surveillance and control, which could hinder legitimate commercial activities, restrict innovation or infringe on personal freedoms.

## 3.1.3 Time, operational and cost constraints

Delay in the deployment of hardware-enabled governance mechanisms may significantly reduce their usefulness and impact. Hardware-enabled mechanisms can help to address existing policy needs in areas such as verification of compliance with reporting requirements and export controls. They may play a critical role in enabling international agreements on responsible AI development. Further compounding the urgency of this issue is that chips without hardware-enabled mechanisms are currently being produced in increasingly large quantities, in response to rapidly growing demand (TechInsights, 2024). The longer it takes to develop and implement, the larger the pool of chips without hardware-enabled mechanisms, which are more challenging to govern, will grow. Therefore, timeliness in the development of mechanisms that are ready for deployment at scale is of critical importance. In this context, approaches that require significant changes to the design of AI accelerators or other AI hardware appear less promising, as they could require several years to progress to production. Conversely, approaches that allow retrofitting to the existing stock of AI accelerators, or some subset of these, are especially valuable.

**Mechanisms should be implemented with minimal disruption to the operation of AI hardware.** Hardware-enabled mechanisms need to be usable in high performance AI settings. Hardware-enabled mechanisms should make allowance for the thermal properties of AI accelerators which result in stringent cooling requirements. This may present a particular challenge to the development of tamper-resistant enclosures. In addition, many frontier AI developers are seeking to improve their cybersecurity through measures such as airgapping (Nevo et al., 2024), which hardware-enabled mechanisms should accommodate when possible. Sometimes, it will not be possible for hardware-enabled mechanism designers to accommodate all of the preferences of frontier AI developers. For example, anti-tampering solutions might include physical enclosures for chips that prevent developers from physically accessing chips to perform maintenance and address hardware failures. These costs may be worthwhile, but should be carefully considered and minimized.

False alerts from certain mechanisms or functionality, such as tamper-responsive enclosures, could interfere with training. Even if they are rare for any given chip, in a cluster of thousands of AI chips a small rate of false alerts could still present meaningful operational challenges. For chip designers and users to adopt the mechanisms, they will therefore need to be shown to be highly reliable and to have acceptable impact on operations.

Hardware-enabled mechanisms must be economically viable to include. Incorporating secure hardware-enabled mechanisms into chips will inevitably add costs, both through the additional research and testing that will be required and through the cost of any extra hardware or software components, if required. Leading-edge AI chips are already expensive, so it is plausible that these additional features would not lead to a large percentage increase in costs. Nevertheless, mechanisms will need to be economically viable to include over the long term for designers and users to adopt them.

#### 3.1.4 Adaptability to future technological changes

Mechanisms will need to be adaptable to a variety of designs and suppliers. AI hardware designs are likely to continue to evolve over time. Novel designs that potentially diverge significantly from existing ones may be introduced,

both from current market leaders and from other companies. While the market for AI accelerators is currently highly concentrated under Nvidia's market leadership, the recent proliferation of chip design projects from large technology companies such as Amazon, Microsoft and Meta and AI developers such as OpenAI is part of a trend towards greater diversification and fragmentation (TheVerge, 2025). It is therefore important not to overfit any hardware-enabled mechanisms to the features of the most prevalent chips today and to maintain flexibility to ensure that they can be made compatible with future designs.

Techniques used for AI development will also likely continue to evolve over time, which could have important implications for AI governance (OpenAI, 2024, Gu and Dao, 2023). Changes in approaches to AI training and inference could result in shifts in how AI infrastructure is designed, which metrics are most relevant for regulators to be tracking, and in other areas (Heim et al., 2024). This enhances the value of flexible mechanisms that can be adapted to a wide range of potential future AI chip designs or configurations of AI training devices.

## 3.2 Physical Tampering

#### 3.2.1 Motivation and definitions

**For hardware-enabled mechanisms to be reliable, chips must be protected against successful tampering.** For the mechanisms discussed previously to achieve their aims, it is essential to guard against the possibility that adversaries could tamper with hardware, potentially altering or circumventing its functionality or copying a private key that they could use to report false information.

**Different measures have different levels of robustness to tampering.** While it may be difficult to obtain a perfect guarantee that hardware is impossible to tamper with, some measures represent stronger protections than others. For the purposes of this paper, we use the following definitions:

- Anti-tamper: any measure that makes it more difficult to physically tamper with hardware.

- Tamper-proof: measures that make tampering impossible within the capabilities and budget of any relevant threat actor

- Tamper-resistant: measures that increase the cost of tampering beyond the budgets of some attackers but not all relevant ones

- Tamper-evident: measures that do not prevent tampering, but mean that an inspector can quickly and cheaply notice if an attack has happened.

- Tamper-respondent: measures taken in response to detected tampering, such as deleting keys if the enclosure is opened.

For some research domains, it will be useful if these terms are defined more rigorously. Future work should explore the range of tamper-related definitions more formally with an information processing perspective on confidentiality, integrity, availability, and the categories of goals of each involved actor.

**Some aspects of hardware attacks are becoming easier** (Hu et al., 2020). As technology progresses, the technological means for attacks on hardware are becoming more sophisticated and more accessible. For example, scanning electron microscopes, which can be used to image a chip and extract information about its design and potential vulnerabilities, are getting cheaper. So too are focused ion beams, which are sometimes used in attempts to alter chips after they are already manufactured, by depositing or removing different materials. Side-channel techniques for obtaining information from hardware are also continually improving, with newer methods applying learning-based techniques to defeat established defenses (Batina et al., 2019). Additionally, the failure analysis methods required in semiconductor manufacturing provide a means of inspecting and modifying chip operation, but these same methods make it easier for attackers to do the same.